イーサネット PHY チップ テクノロジー ホワイト ペーパー

世界市場規模

2023年:約12億ドル(データソース:Yole Développement) 2028年の予測:25億ドル以上(CAGR 15.8%) 成長ドライバー:データセンターのアップグレード(400G/800G PHY需要) 自動車インテリジェンス(車両あたりのPHY数が1-2から10+に増加) インダストリー4.0(産業用イーサネット普及率が50%を超える)

地域市場分布

北米: 40% (データセンターと自動車エレクトロニクスが牽引) アジア太平洋: 35% (中国が主な成長極、5G 基地局と電気自動車の需要) ヨーロッパ: 20% (インダストリアル 4.0 と自動車産業チェーンの成熟)

市場の競争パターン

北米: 40% (データセンターと自動車エレクトロニクスが牽引) アジア太平洋: 35% (中国が主な成長極、5G 基地局と電気自動車の需要) ヨーロッパ: 20% (インダストリアル 4.0 と自動車産業チェーンの成熟)

今後の動向

1. 技術の方向性:

超高速: 800G PHY (PAM4 変調、シリコンフォトニクス統合) 低消費電力: 3nm プロセス PHY チップ (消費電力 50% 削減) 車載グレード: 10G PHY は L4/L5 自動運転をサポート (2025 年に量産)

2. サプライチェーンの変化:

米国は中国へのハイエンドPHYの輸出を制限し、国内代替のプロセスを加速させている。 TSMC/Samsung は、ハイエンド市場で競争するために 3nm PHY ファウンドリを導入しています。

MAC と物理メディア (銅線ケーブル/光ファイバー) を接続して、安定したネットワーク伝送を確保します。

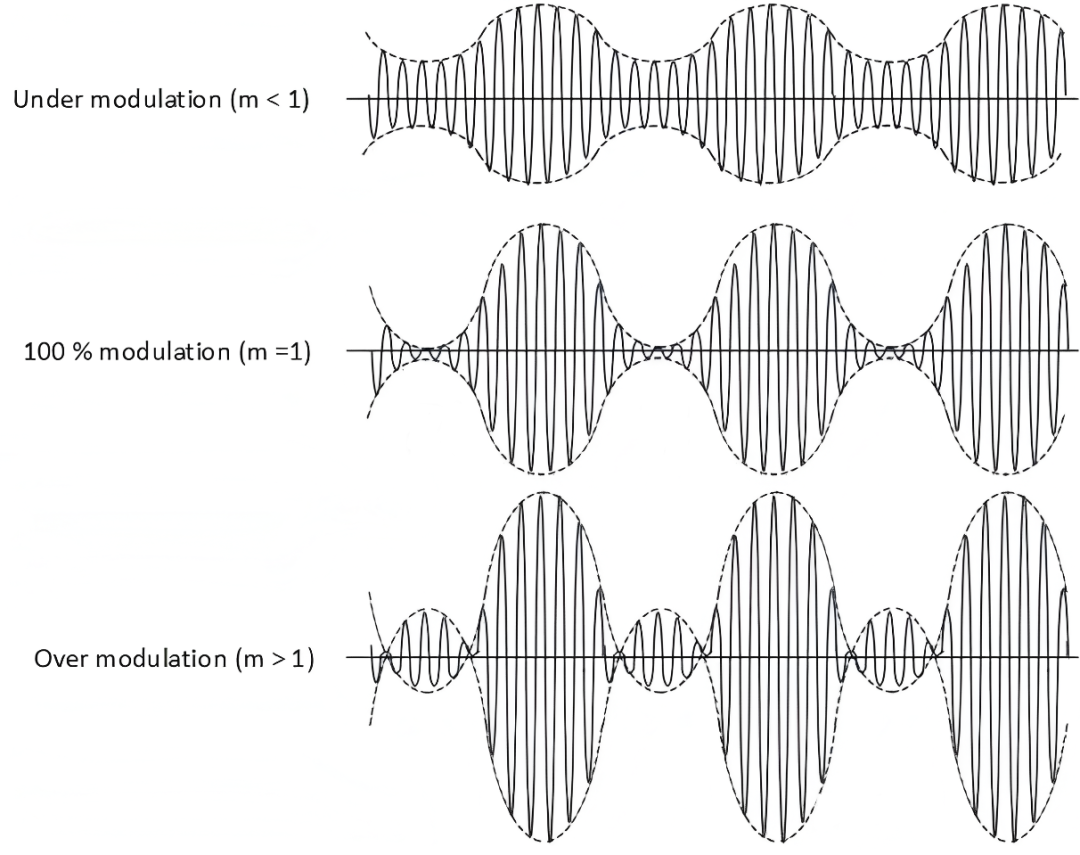

1. 信号調整

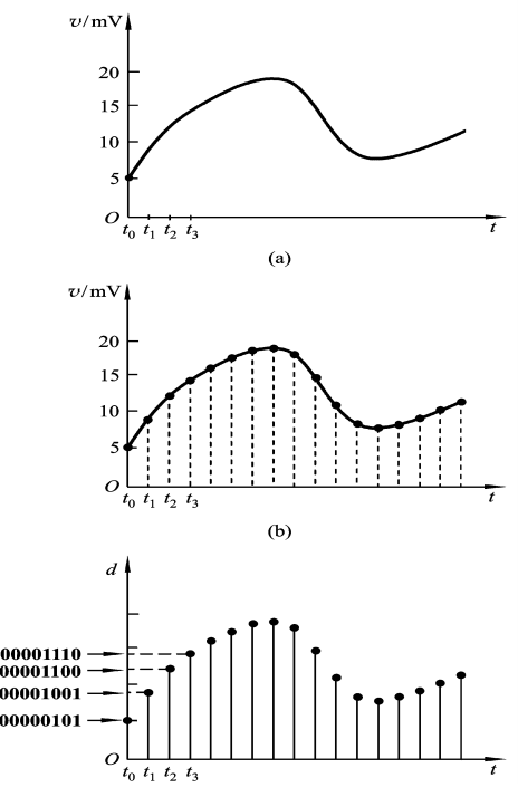

MAC 層によって送信されたパラレル データをシリアル ビット ストリームに変換し、受信したアナログ信号をサンプリングしてデコードしてデジタル信号に復元します。

2. データのエンコード/デコード

長距離ケーブルにおける高周波信号の減衰を補償し、符号間干渉(ISI)を除去し、信号波形を復元します。

3. 物理メディアインターフェイス

ツイストペア + 光ファイバー + バックプレーン; ESD保護とコモンモード抑制を内蔵。

4. 電源管理と診断

アイドル時に未使用のトランシーバー チャネルを閉じると、低電力モードで消費電力を 70% 削減できます。ケーブルの断線/短絡/インピーダンス異常を検出し、リンク状態を読み取る機能を備えています。

5. リンクネゴシエーション レートに適応する

FLP (Fast Link Pulse) を通じてピア デバイスと最適なレート (10/100/1000Mbps) をネゴシエートし、再接続を迅速に確立します。

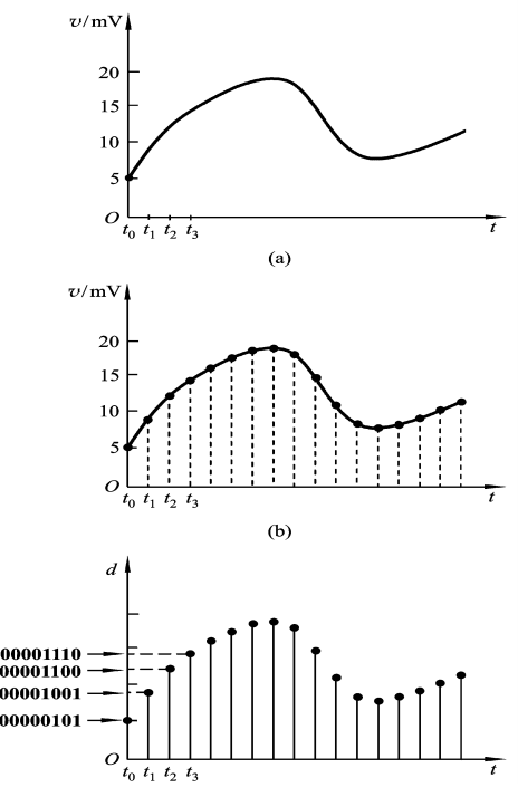

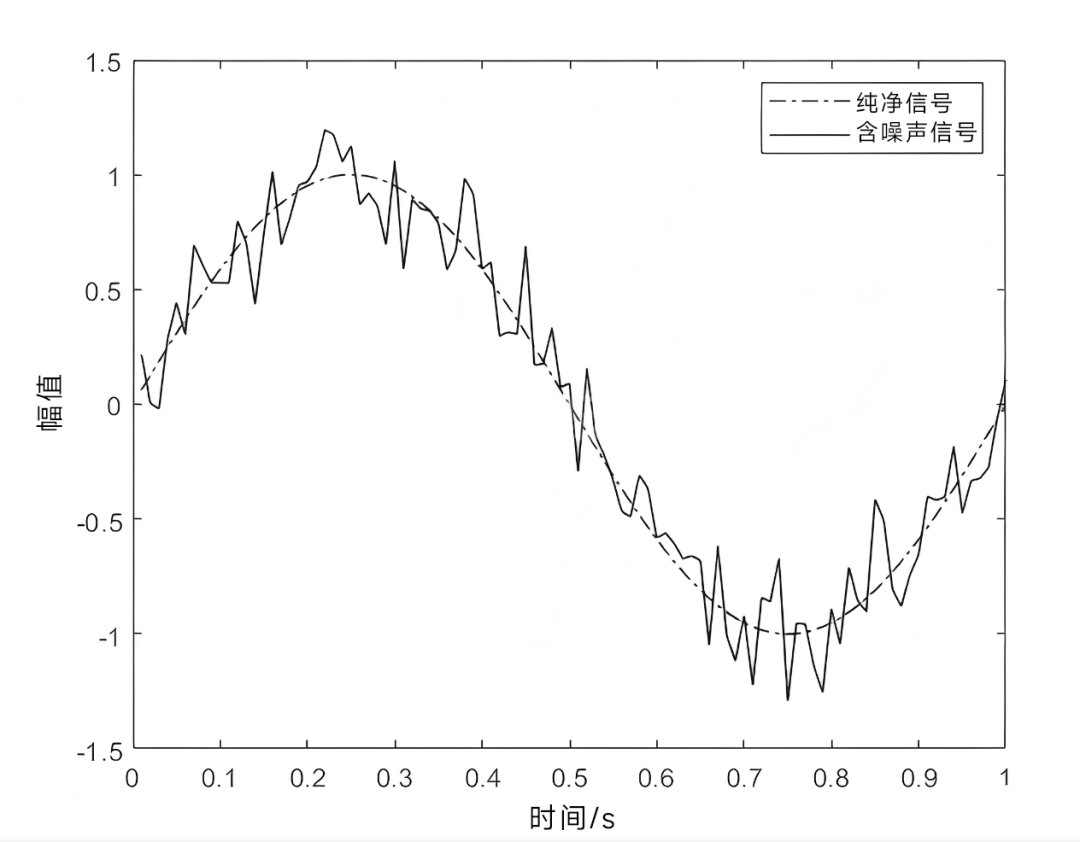

信号調整/データのエンコードとデコード

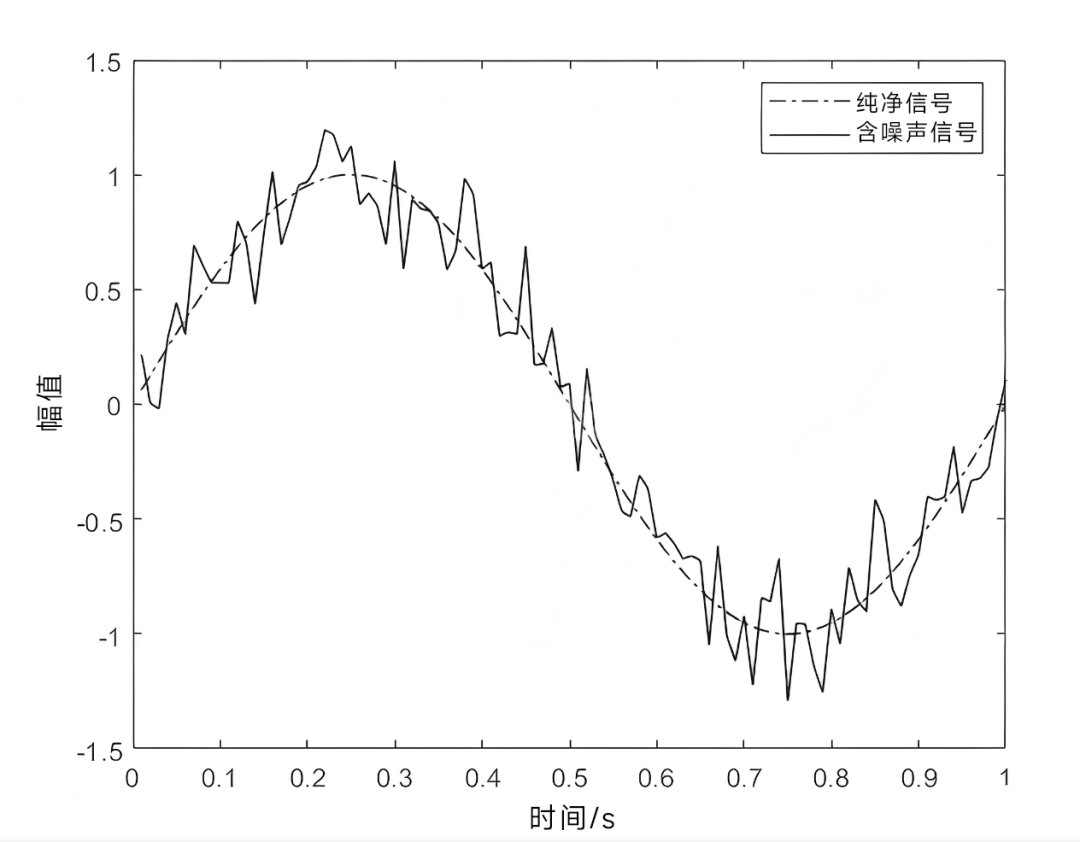

1. 信号調整の必要性

·信号振幅調整:収集を容易にするための信号増幅; ·信号対雑音比の改善:電気信号のノイズ干渉を除去; ·信号変換:必要なパラメータの観察に便利な関数関係による信号変換を実現; ·機器要件を満たす:信号マッチング; ·長距離伝送の実現:長距離伝送中の干渉防止; ·機器の保護:高電圧信号を測定する際にバックエンド機器を保護;

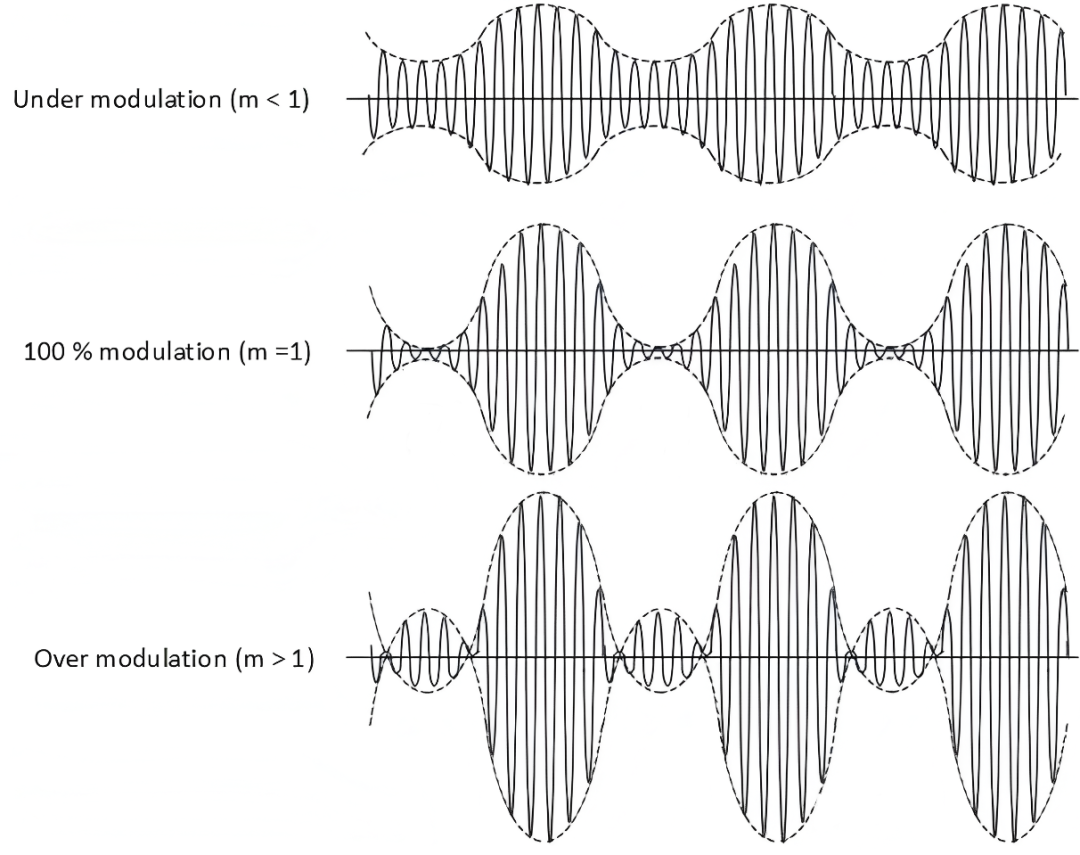

2. 信号調整プロセス (ほとんどの長距離通信に適用可能)

信号増幅 -> フィルタリング -> 信号変換 -> 線形化 -> 絶縁保護 -> 変調および復調 -> レベル調整。

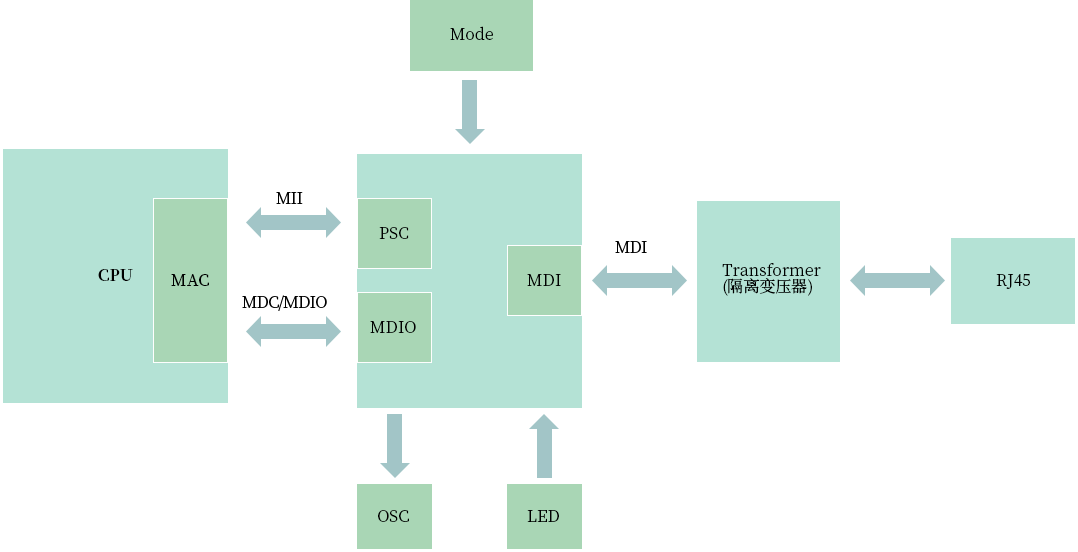

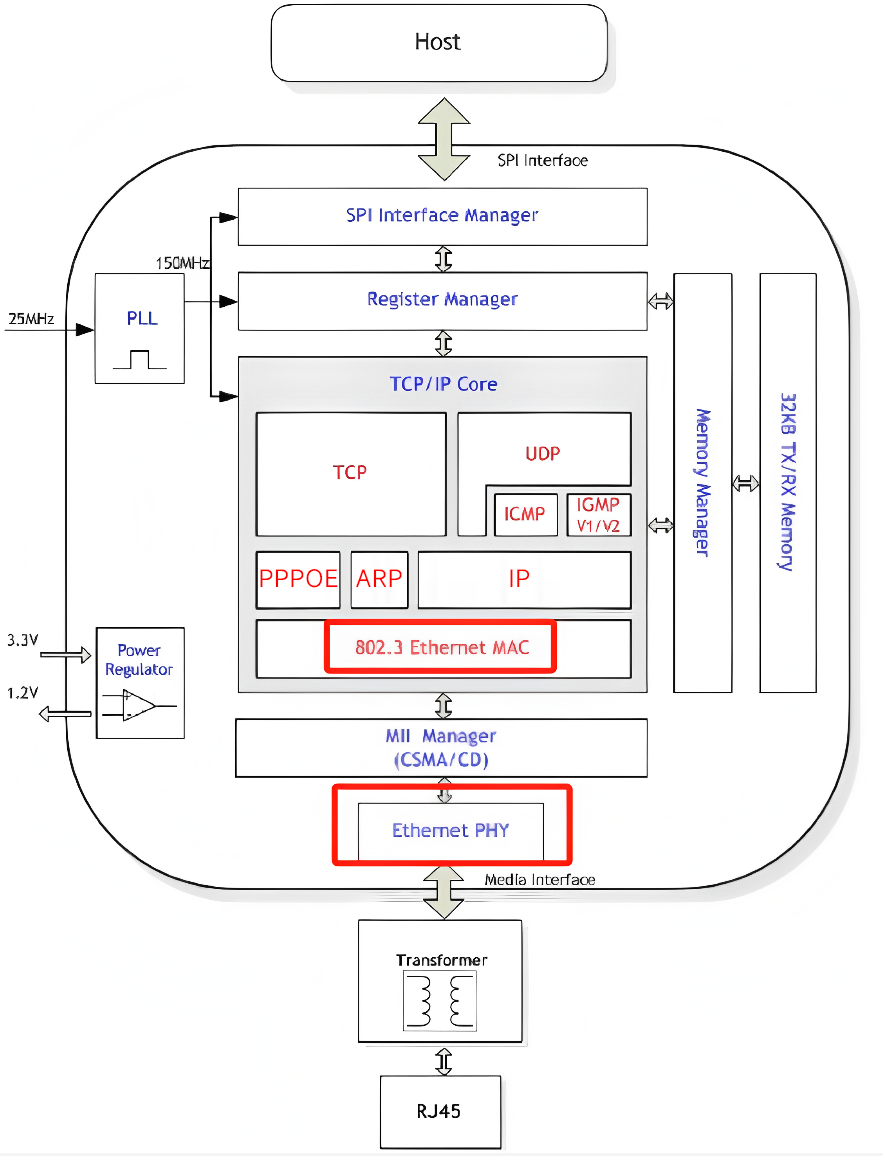

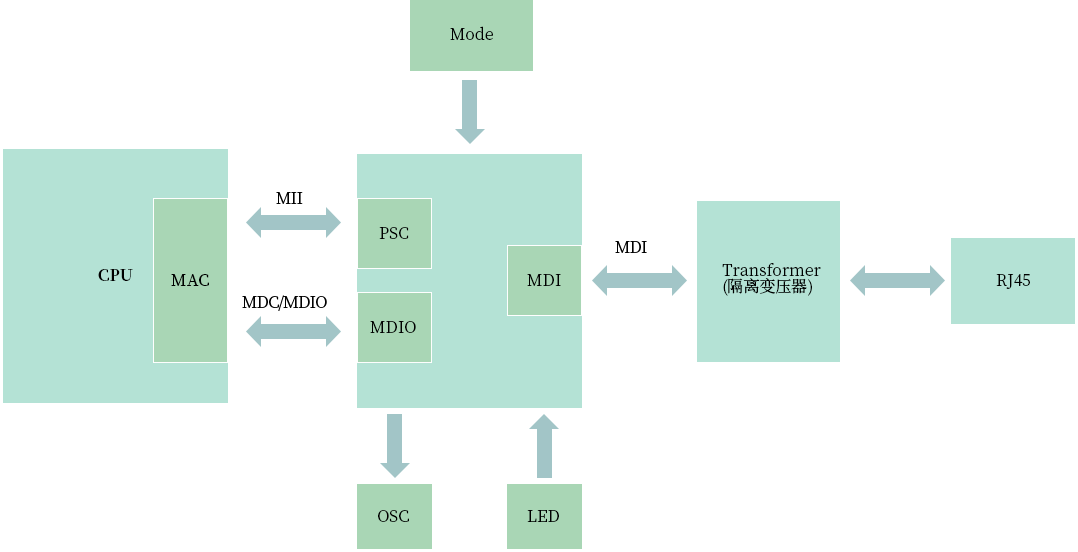

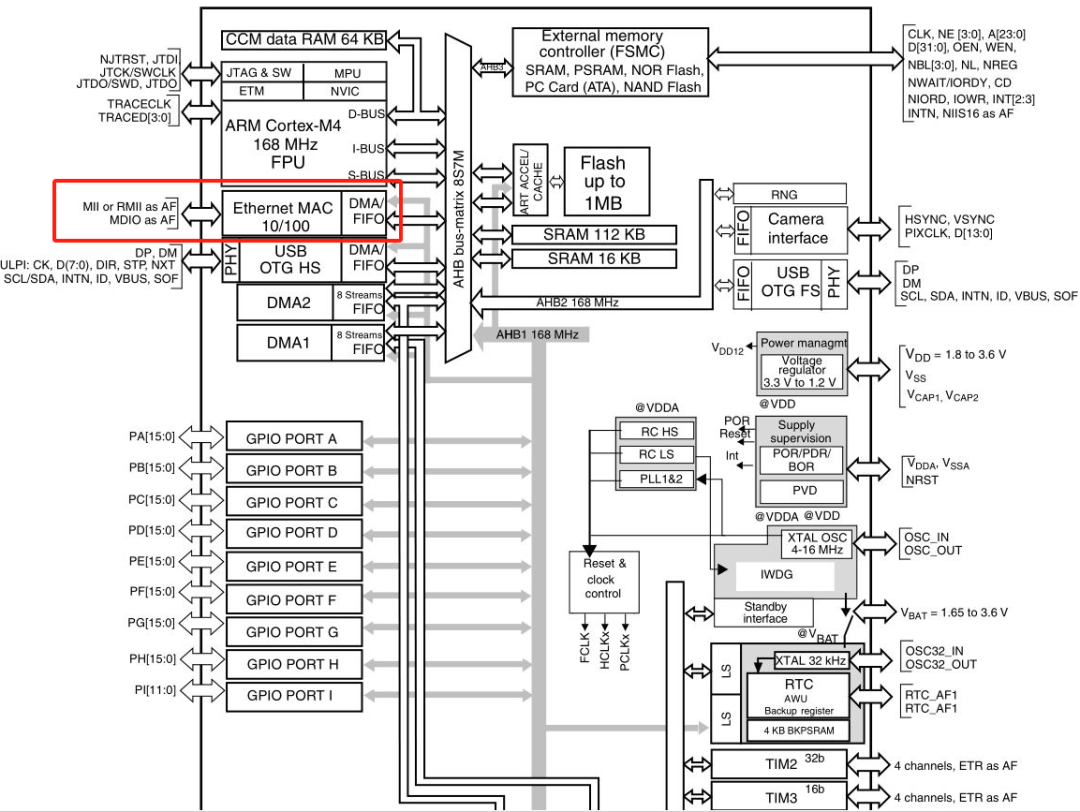

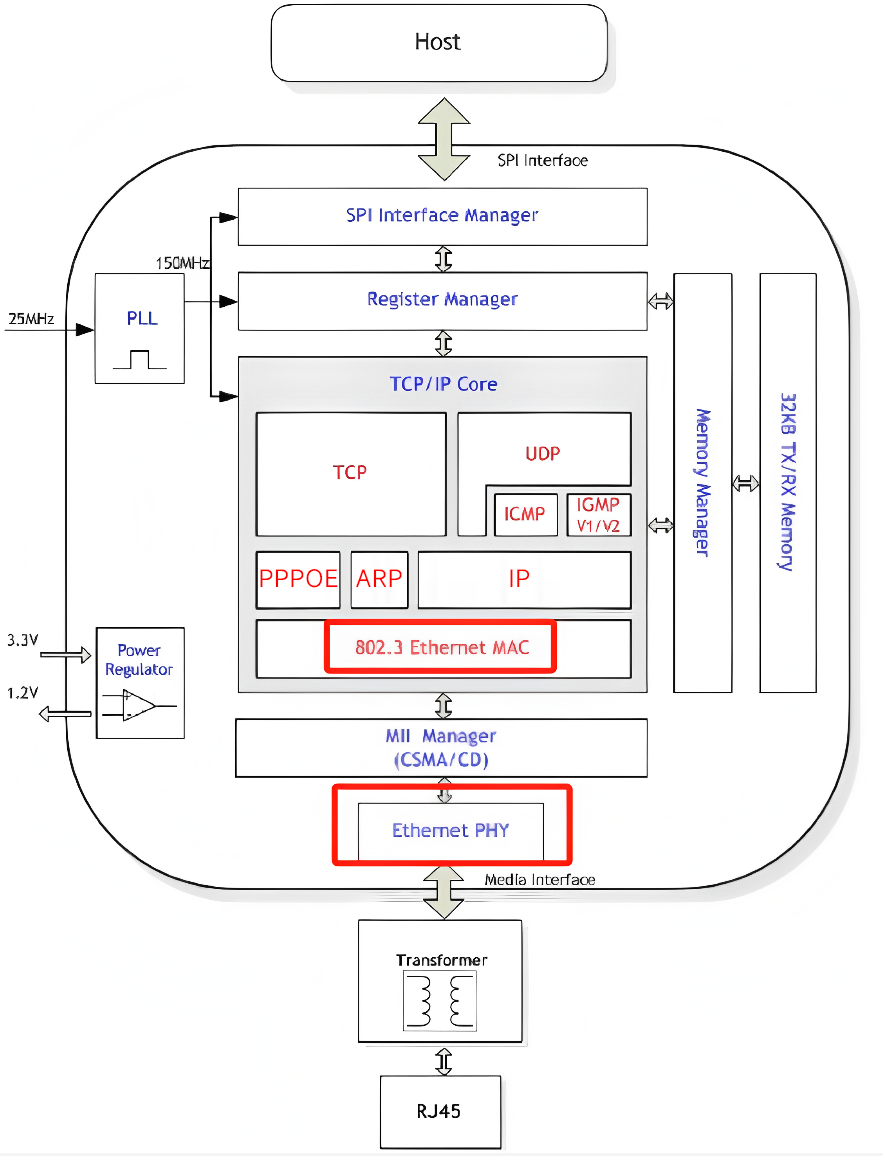

構造図

PHYチップ

PHY (物理層) チップは物理層のコア コンポーネントであり、イーサネット信号の送受信を担当します。主な機能は次のとおりです。

• 信号変換: デジタル信号をネットワーク ケーブル伝送に適したアナログ信号に変換 (送信) し、アナログ信号をデジタル信号に変換 (受信) します。

• 電気的保護: ネットワーク変圧器を介して追加の電気絶縁を提供し、落雷や電磁干渉などの外部要因による損傷から PHY チップを保護します。

ネットワークトランス

• 信号結合と送信: PHY チップによる差動信号出力を強化し、差動モード結合を通じてネットワーク ケーブルの他端に送信します。

• 電気的絶縁: PHY チップとネットワーク ケーブル間の DC レベル差を絶縁し、異なるデバイス間の電圧差によるデバイスの損傷を防ぎます。

• インピーダンスマッチング: 信号源、負荷、伝送ライン間のインピーダンスマッチングを確保し、信号反射とビットエラーを低減します。

• 電磁干渉抑制: コモンモードノイズを抑制し、コモンモードチョーク (CMC) によって電磁干渉を軽減します。

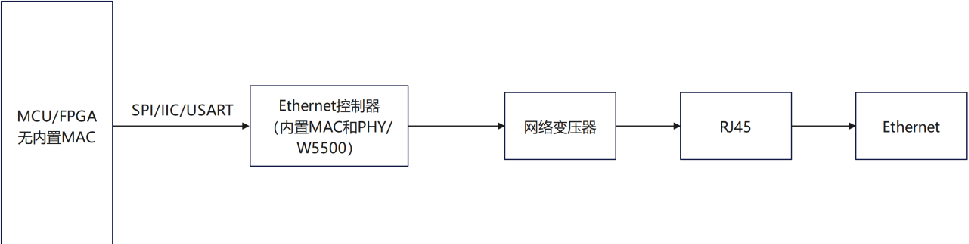

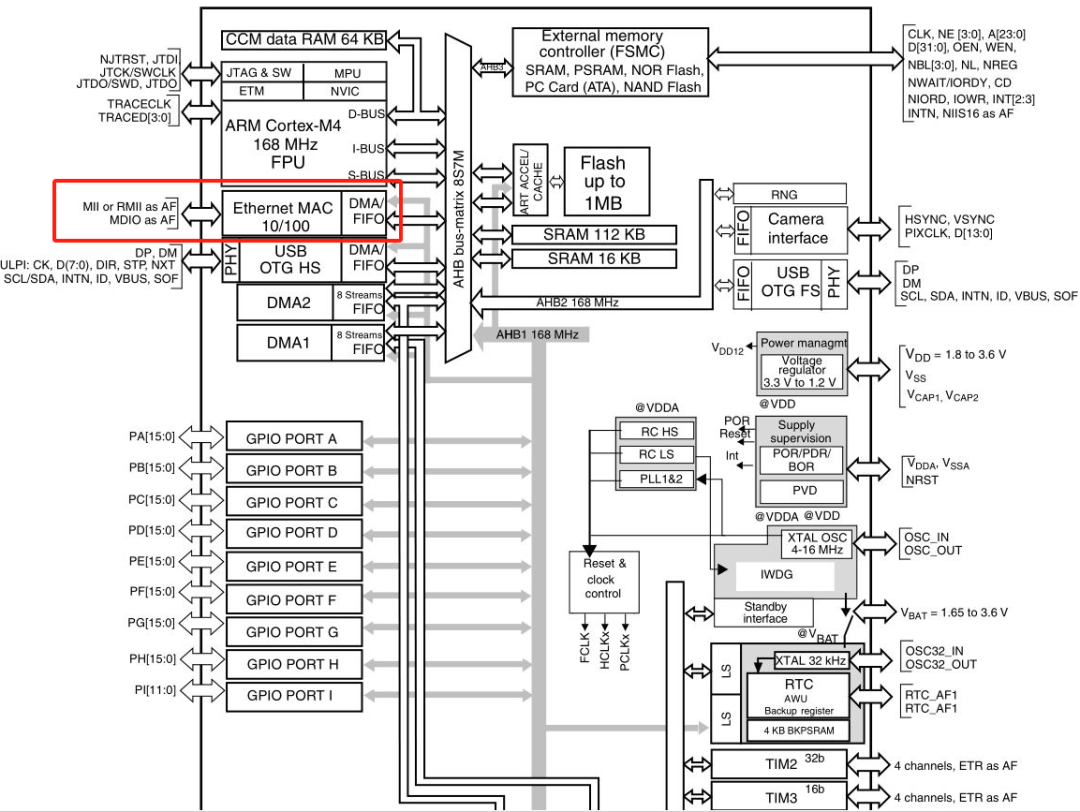

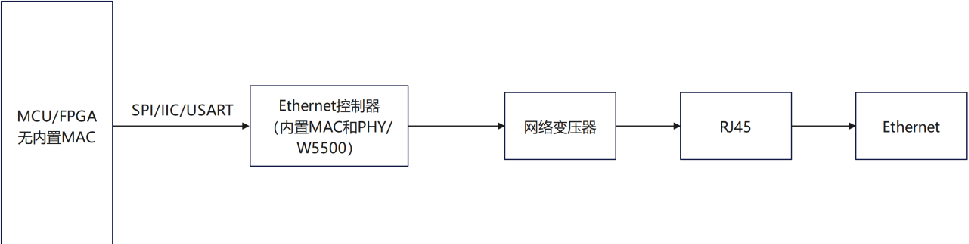

上記 3 つの部分は、必ずしもすべてが独立したチップであるとは限りません。主に次のような状況があります。MAC と PHY が CPU 内に統合されているため、より困難です。 MAC は CPU 内に統合され、PHY は独立したチップを使用します (主流のソリューション)。 MAC と PHY は CPU に統合されておらず、MAC と PHY は独立したチップまたは統合チップ (ハイエンド用途) を使用します。

パラメータ

1. レートサポート

• サポートされるレート範囲: PHY チップは、10 Mbps、100 Mbps、1 Gbps、10 Gbps など、ターゲット アプリケーションで必要なイーサネット レートをサポートする必要があります。

• アダプティブ レート ネゴシエーション: 自動ネゴシエーション機能をサポートし、ピア デバイスの機能に応じて最適なレート (10/100/1000 Mbps など) と二重モード (全二重/半二重) を自動的に選択できます。

2. インターフェース規格

PHY チップは上位 MAC 層と互換性がある必要があります。一般的なインターフェイスには次のものがあります。

• MII: 10/100 Mbps イーサネットに適用されます。

• RMII: ピンの数が少ない MII の簡易バージョンで、10/100 Mbps に適しています。

• GMII: 1 Gbps レートをサポートします。

• RGMII: ピン数が少ない GMII の簡易バージョンで、1 Gbps に適しています。

• SGMII: シリアル インターフェイス。少ないピンで 1 Gbps に適しています。

• 物理メディア インターフェイス (MDI): ツイスト ペア (BASE-T)、ファイバ (BASE-X)、シングル ツイスト ペア (BASE-T1) など、サポートされている物理メディア タイプ。

3. 伝送距離

• 伝送距離: アプリケーション要件に応じて、必要な伝送距離をサポートする PHY チップを選択します。たとえば、1000BASE-T (ギガビット イーサネット) は最大 100 メートルのツイスト ペア伝送をサポートしますが、ファイバー PHY (1000BASE-LX など) はより長い距離をサポートできます。

4. 消費電力

• 消費電力レベル: 低電力設計は、特に高密度デバイス (スイッチなど) やモバイル デバイスの省エネと熱管理にとって重要です。たとえば、EEE (Energy Efficient Ethernet) 規格をサポートする PHY チップは、アイドル時の消費電力を削減できます。

• 熱設計: 特に高温環境または高密度アプリケーションにおける PHY チップの放熱要件を考慮します。

5. 信頼性と安定性

• 電気的絶縁: ネットワークトランスによって電気的絶縁が実現され、落雷や電磁干渉などの外部要因による損傷から PHY チップを保護します。

• 耐干渉性能: PHY チップは良好な電磁両立性 (EMC) を備え、産業環境における電磁干渉に耐えることができる必要があります。たとえば、CISPR 32 や IEC 61000-4-2 などの規格に準拠する必要があります。

• 動作温度範囲: 工業用-グレードの PHY チップは通常、過酷な環境に適応するために広い温度範囲 (-40°C85°C など) をサポートします。

6. 特別な機能

• PoE サポート: アプリケーション (IP カメラ、ワイヤレス アクセス ポイントなど) でイーサネット ケーブルから電力を供給する必要がある場合は、PoE (IEEE 80) をサポートするチップを選択する必要があります。

• 診断機能: リンク状態の検出や信号品質の監視などの機能をサポートし、ネットワークの保守とトラブルシューティングを容易にします。 • セキュリティ機能: 一部のアプリケーションでは、PHY チップが暗号化通信や認証機能などのセキュリティ機能をサポートする必要がある場合があります。

アプリケーションシナリオ

(1) 10/100Mbps PHY

アプリケーションシナリオ: 産業用制御: PLC、センサーネットワーク (Modbus TCP など) スマートホーム: スマートソケット、低電力 IoT デバイス (Zigbee ゲートウェイなど) オンボード診断: OBD-II インターフェイス (100BASE-T1)

(2) 1Gbps PHY

アプリケーションシナリオ: 家庭用電化製品: 4K TV、NAS ストレージ 産業用カメラ: マシンビジョン (リアルタイム画像伝送) エンタープライズネットワーク: ギガビットスイッチ、ルーター

(3) 2.5G/5G PHY (マルチ-ギガビット)

アプリケーションシナリオ: 産業用制御: PLC、センサーネットワーク (Modbus TCP など) スマートホーム: スマートソケット、低電力 IoT デバイス (Zigbee ゲートウェイなど) オンボード診断: OBD-II インターフェイス (100BASE-T1)

(4) 10G/25G PHY

アプリケーション シナリオ: データ センター: サーバー相互接続 (SFP+/QSFP28) 5G 基地局: フロントホール ネットワーク (eCPRI over 25G) 超-高解像度- ビデオ制作: 8K ビデオ リアルタイム伝送

(5) 40G/100G 以上の PHY

アプリケーションシナリオ: AI/スーパーコンピューティングクラスタ: GPU/TPU 相互接続 (InfiniBand 代替) コアバックボーンネットワーク: 首都圏ネットワーク/データセンター間相互接続 光通信: CPRI/OBSAI ファイバーフロントホール

デザインの選択

(1) MII (メディア独立インターフェース)

速度: 10/100Mbps ピン数: 16+ アプリケーションシナリオ: 初期の組み込みシステム (ARM9 産業用制御ボードなど) 複雑さの低い設計 (外部 MAC コントローラーが必要) 短所: 複雑な配線、段階的に RMII に置き換えられる

(2) RMII(リデュースドMII)

レート: 10/100Mbps ピン数: 6 (データ + クロック) アプリケーションシナリオ: コスト-敏感なデバイス (ホームルーターなど) スペース- 制約のある設計 (IoT モジュール) 利点: 配線の簡素化、50MHz クロックのサポート

(3) RGMII (Reduced Gigabit MII)

レート: 1Gbps ピン数: 12 (デュアル-エッジ サンプリング) アプリケーション シナリオ: ギガビット スイッチ、産業用ゲートウェイは 100M/1G 柔軟な設計と互換性がある必要がある 重要なポイント: 厳密なタイミング制御が必要 (±1ns 偏差許容値)

(4) SGMII(シリアルギガビットMII)

速度: 1G/2.5Gbps ピン数: 2 (差動ペア) アプリケーションシナリオ: 長距離基板間接続 (SerDes 経由) FPGA と PHY 間の高速通信 利点: 強力な干渉防止、バックプレーン伝送のサポート

(5)USXGMII(ウルトラスピードMII)

レート: 10Gbps ピンの数: 4 (差動ペア) アプリケーション シナリオ: マルチ-レート スイッチ (10M/100M/1G/10G アダプティブ) データ センター リーフ-スパイン アーキテクチャ 特徴: 低ジッター クロックが必要 (<0.5ps RMS)

利点

適切な信頼性戦略をオンデマンドでカスタマイズ可能

製品の信頼性テストは、次の国際規格に厳密に準拠しています。

2023年:約12億ドル(データソース:Yole Développement) 2028年の予測:25億ドル以上(CAGR 15.8%) 成長ドライバー:データセンターのアップグレード(400G/800G PHY需要) 自動車インテリジェンス(車両あたりのPHY数が1-2から10+に増加) インダストリー4.0(産業用イーサネット普及率が50%を超える)

地域市場分布

北米: 40% (データセンターと自動車エレクトロニクスが牽引) アジア太平洋: 35% (中国が主な成長極、5G 基地局と電気自動車の需要) ヨーロッパ: 20% (インダストリアル 4.0 と自動車産業チェーンの成熟)

市場の競争パターン

北米: 40% (データセンターと自動車エレクトロニクスが牽引) アジア太平洋: 35% (中国が主な成長極、5G 基地局と電気自動車の需要) ヨーロッパ: 20% (インダストリアル 4.0 と自動車産業チェーンの成熟)

今後の動向

1. 技術の方向性:

超高速: 800G PHY (PAM4 変調、シリコンフォトニクス統合) 低消費電力: 3nm プロセス PHY チップ (消費電力 50% 削減) 車載グレード: 10G PHY は L4/L5 自動運転をサポート (2025 年に量産)

2. サプライチェーンの変化:

米国は中国へのハイエンドPHYの輸出を制限し、国内代替のプロセスを加速させている。 TSMC/Samsung は、ハイエンド市場で競争するために 3nm PHY ファウンドリを導入しています。

製品の特徴

MAC と物理メディア (銅線ケーブル/光ファイバー) を接続して、安定したネットワーク伝送を確保します。

1. 信号調整

MAC 層によって送信されたパラレル データをシリアル ビット ストリームに変換し、受信したアナログ信号をサンプリングしてデコードしてデジタル信号に復元します。

2. データのエンコード/デコード

長距離ケーブルにおける高周波信号の減衰を補償し、符号間干渉(ISI)を除去し、信号波形を復元します。

3. 物理メディアインターフェイス

ツイストペア + 光ファイバー + バックプレーン; ESD保護とコモンモード抑制を内蔵。

4. 電源管理と診断

アイドル時に未使用のトランシーバー チャネルを閉じると、低電力モードで消費電力を 70% 削減できます。ケーブルの断線/短絡/インピーダンス異常を検出し、リンク状態を読み取る機能を備えています。

5. リンクネゴシエーション レートに適応する

FLP (Fast Link Pulse) を通じてピア デバイスと最適なレート (10/100/1000Mbps) をネゴシエートし、再接続を迅速に確立します。

信号調整/データのエンコードとデコード

1. 信号調整の必要性

·信号振幅調整:収集を容易にするための信号増幅; ·信号対雑音比の改善:電気信号のノイズ干渉を除去; ·信号変換:必要なパラメータの観察に便利な関数関係による信号変換を実現; ·機器要件を満たす:信号マッチング; ·長距離伝送の実現:長距離伝送中の干渉防止; ·機器の保護:高電圧信号を測定する際にバックエンド機器を保護;

2. 信号調整プロセス (ほとんどの長距離通信に適用可能)

信号増幅 -> フィルタリング -> 信号変換 -> 線形化 -> 絶縁保護 -> 変調および復調 -> レベル調整。

構造図

PHYチップ

PHY (物理層) チップは物理層のコア コンポーネントであり、イーサネット信号の送受信を担当します。主な機能は次のとおりです。

• 信号変換: デジタル信号をネットワーク ケーブル伝送に適したアナログ信号に変換 (送信) し、アナログ信号をデジタル信号に変換 (受信) します。

• 電気的保護: ネットワーク変圧器を介して追加の電気絶縁を提供し、落雷や電磁干渉などの外部要因による損傷から PHY チップを保護します。

ネットワークトランス

• 信号結合と送信: PHY チップによる差動信号出力を強化し、差動モード結合を通じてネットワーク ケーブルの他端に送信します。

• 電気的絶縁: PHY チップとネットワーク ケーブル間の DC レベル差を絶縁し、異なるデバイス間の電圧差によるデバイスの損傷を防ぎます。

• インピーダンスマッチング: 信号源、負荷、伝送ライン間のインピーダンスマッチングを確保し、信号反射とビットエラーを低減します。

• 電磁干渉抑制: コモンモードノイズを抑制し、コモンモードチョーク (CMC) によって電磁干渉を軽減します。

上記 3 つの部分は、必ずしもすべてが独立したチップであるとは限りません。主に次のような状況があります。MAC と PHY が CPU 内に統合されているため、より困難です。 MAC は CPU 内に統合され、PHY は独立したチップを使用します (主流のソリューション)。 MAC と PHY は CPU に統合されておらず、MAC と PHY は独立したチップまたは統合チップ (ハイエンド用途) を使用します。

パラメータ

1. レートサポート

• サポートされるレート範囲: PHY チップは、10 Mbps、100 Mbps、1 Gbps、10 Gbps など、ターゲット アプリケーションで必要なイーサネット レートをサポートする必要があります。

• アダプティブ レート ネゴシエーション: 自動ネゴシエーション機能をサポートし、ピア デバイスの機能に応じて最適なレート (10/100/1000 Mbps など) と二重モード (全二重/半二重) を自動的に選択できます。

2. インターフェース規格

PHY チップは上位 MAC 層と互換性がある必要があります。一般的なインターフェイスには次のものがあります。

• MII: 10/100 Mbps イーサネットに適用されます。

• RMII: ピンの数が少ない MII の簡易バージョンで、10/100 Mbps に適しています。

• GMII: 1 Gbps レートをサポートします。

• RGMII: ピン数が少ない GMII の簡易バージョンで、1 Gbps に適しています。

• SGMII: シリアル インターフェイス。少ないピンで 1 Gbps に適しています。

• 物理メディア インターフェイス (MDI): ツイスト ペア (BASE-T)、ファイバ (BASE-X)、シングル ツイスト ペア (BASE-T1) など、サポートされている物理メディア タイプ。

3. 伝送距離

• 伝送距離: アプリケーション要件に応じて、必要な伝送距離をサポートする PHY チップを選択します。たとえば、1000BASE-T (ギガビット イーサネット) は最大 100 メートルのツイスト ペア伝送をサポートしますが、ファイバー PHY (1000BASE-LX など) はより長い距離をサポートできます。

4. 消費電力

• 消費電力レベル: 低電力設計は、特に高密度デバイス (スイッチなど) やモバイル デバイスの省エネと熱管理にとって重要です。たとえば、EEE (Energy Efficient Ethernet) 規格をサポートする PHY チップは、アイドル時の消費電力を削減できます。

• 熱設計: 特に高温環境または高密度アプリケーションにおける PHY チップの放熱要件を考慮します。

5. 信頼性と安定性

• 電気的絶縁: ネットワークトランスによって電気的絶縁が実現され、落雷や電磁干渉などの外部要因による損傷から PHY チップを保護します。

• 耐干渉性能: PHY チップは良好な電磁両立性 (EMC) を備え、産業環境における電磁干渉に耐えることができる必要があります。たとえば、CISPR 32 や IEC 61000-4-2 などの規格に準拠する必要があります。

• 動作温度範囲: 工業用-グレードの PHY チップは通常、過酷な環境に適応するために広い温度範囲 (-40°C85°C など) をサポートします。

6. 特別な機能

• PoE サポート: アプリケーション (IP カメラ、ワイヤレス アクセス ポイントなど) でイーサネット ケーブルから電力を供給する必要がある場合は、PoE (IEEE 80) をサポートするチップを選択する必要があります。

• 診断機能: リンク状態の検出や信号品質の監視などの機能をサポートし、ネットワークの保守とトラブルシューティングを容易にします。 • セキュリティ機能: 一部のアプリケーションでは、PHY チップが暗号化通信や認証機能などのセキュリティ機能をサポートする必要がある場合があります。

アプリケーションシナリオ

(1) 10/100Mbps PHY

アプリケーションシナリオ: 産業用制御: PLC、センサーネットワーク (Modbus TCP など) スマートホーム: スマートソケット、低電力 IoT デバイス (Zigbee ゲートウェイなど) オンボード診断: OBD-II インターフェイス (100BASE-T1)

(2) 1Gbps PHY

アプリケーションシナリオ: 家庭用電化製品: 4K TV、NAS ストレージ 産業用カメラ: マシンビジョン (リアルタイム画像伝送) エンタープライズネットワーク: ギガビットスイッチ、ルーター

(3) 2.5G/5G PHY (マルチ-ギガビット)

アプリケーションシナリオ: 産業用制御: PLC、センサーネットワーク (Modbus TCP など) スマートホーム: スマートソケット、低電力 IoT デバイス (Zigbee ゲートウェイなど) オンボード診断: OBD-II インターフェイス (100BASE-T1)

(4) 10G/25G PHY

アプリケーション シナリオ: データ センター: サーバー相互接続 (SFP+/QSFP28) 5G 基地局: フロントホール ネットワーク (eCPRI over 25G) 超-高解像度- ビデオ制作: 8K ビデオ リアルタイム伝送

(5) 40G/100G 以上の PHY

アプリケーションシナリオ: AI/スーパーコンピューティングクラスタ: GPU/TPU 相互接続 (InfiniBand 代替) コアバックボーンネットワーク: 首都圏ネットワーク/データセンター間相互接続 光通信: CPRI/OBSAI ファイバーフロントホール

デザインの選択

(1) MII (メディア独立インターフェース)

速度: 10/100Mbps ピン数: 16+ アプリケーションシナリオ: 初期の組み込みシステム (ARM9 産業用制御ボードなど) 複雑さの低い設計 (外部 MAC コントローラーが必要) 短所: 複雑な配線、段階的に RMII に置き換えられる

(2) RMII(リデュースドMII)

レート: 10/100Mbps ピン数: 6 (データ + クロック) アプリケーションシナリオ: コスト-敏感なデバイス (ホームルーターなど) スペース- 制約のある設計 (IoT モジュール) 利点: 配線の簡素化、50MHz クロックのサポート

(3) RGMII (Reduced Gigabit MII)

レート: 1Gbps ピン数: 12 (デュアル-エッジ サンプリング) アプリケーション シナリオ: ギガビット スイッチ、産業用ゲートウェイは 100M/1G 柔軟な設計と互換性がある必要がある 重要なポイント: 厳密なタイミング制御が必要 (±1ns 偏差許容値)

(4) SGMII(シリアルギガビットMII)

速度: 1G/2.5Gbps ピン数: 2 (差動ペア) アプリケーションシナリオ: 長距離基板間接続 (SerDes 経由) FPGA と PHY 間の高速通信 利点: 強力な干渉防止、バックプレーン伝送のサポート

(5)USXGMII(ウルトラスピードMII)

レート: 10Gbps ピンの数: 4 (差動ペア) アプリケーション シナリオ: マルチ-レート スイッチ (10M/100M/1G/10G アダプティブ) データ センター リーフ-スパイン アーキテクチャ 特徴: 低ジッター クロックが必要 (<0.5ps RMS)

利点

適切な信頼性戦略をオンデマンドでカスタマイズ可能

製品の信頼性テストは、次の国際規格に厳密に準拠しています。

AEC (オートモーティブ エレクトロニクス協議会)

JEDEC(共同電子デバイス工学協議会)

MIL(軍用規格)

IEC (国際電気技術委員会)

製品の品質を万全にするために、次の5つの側面から製品の信頼性を確保しています。

プロセスの信頼性

包装プロセスの信頼性

製品の信頼性

量産信頼性監視

故障解析

共有する

関連リンク

あなたも好きかもしれません

前の記事

次の記事

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

Subscribe

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy