イーサネット通信異常のトラブルシューティング ガイド: PHY およびネットワーク トランスの選択と配線設計の問題の詳細な分析

イーサネット通信異常のトラブルシューティング ガイド: PHY およびネットワーク トランスの選択と配線設計の問題の詳細な分析

——ハードウェア設計のソースからリンク障害を特定します。

─────────────────

1. Ethernet通信でよくある異常現象の解析と設計との関連性

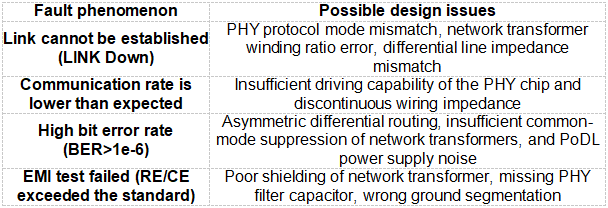

イーサネット通信の異常は、通常、リンク確立の失敗、頻繁なパケット損失、レート低下、高いビット エラー レート、過剰な EMI 干渉として現れます。これらの問題のほとんどは、ハードウェア設計における PHY チップ、ネットワーク トランス (ネット トランス) 構成、および配線ソリューションの選択に直接関係しています。

代表的な異常現象と設計上の欠陥一覧表

─────────────────

2. PHYチップの選択が間違っていることによる通信障害

PHY チップは物理層の中核です。選択を誤ると、プロトコルの互換性や信号品質などの問題が発生する可能性があります。

1. プロトコル規格が一致しない

- 例: 産業用機器は 10BASE-T1L PHY チップ (ADI ADIN1100 など) を使用していますが、ネットワーク トランスは 100BASE-TX (巻数比 1:1) のみをサポートしているため、信号結合障害が発生します。

- トラブルシューティングの手順:

- PHY がサポートするプロトコル (IEEE 802.3cg/802.3bw など) を確認します。

- ネットワーク トランスの周波数応答がターゲット周波数帯域をカバーしているかどうかを確認します (たとえば、10BASE-T1L は 1-16MHz をサポートする必要があります)。

- 解決策: ブロードバンド ネットワーク トランス (1-100MHz をサポートする Halo TG110-E055N5 など) に交換します。

2. 電源とレベルの互換性の問題

- ケース: PHY チップの I/O 電圧は 1.8V ですが、3.3V MAC コントローラに接続されているため、信号振幅が不十分になります。

- 主要パラメータの検証:

- PHY の VDDIO 電圧 (1.8V/2.5V/3.3V) は、MAC コントローラーの電圧と一致している必要があります。

- PHY 駆動電流 (20mA 対 10mA など) によって信号伝送距離が決まります。

- デバッグ ツール: オシロスコープを使用して TX+/- を測定します。差動振幅 (標準: ±1V ピーク-トゥ-ピーク)。

3. 温度と ESD 保護が不十分

- ケース: 車載 PHY チップ (TI DP83TC811S-Q1 など) は AEC-Q100 Grade 2 認定を満たしておらず、高温環境でクラッシュします。

- デザインポイント:

- 産業用-グレードのPHYは-40℃~+125℃をサポートする必要があり、車載用PHYはAEC-Q100認証に合格する必要があります。

- PHY インターフェイスに TVS ダイオード (Bourns CDSOT23-SM712 など) を追加して、ESD 保護 (±8kV 以上の接触放電) を強化します。

─────────────────

3. ネットワークトランスの選定と配線設計上の欠陥

ネットワークトランスは信号の結合と絶縁を担当します。設計エラーは信号の歪みや干渉を直接引き起こします。

1. 間違った巻線比

- 検証方法: LCR メーターを使用して、グリッド変圧器の一次/二次インダクタンスを測定します (標準の 1:1 変圧器のインダクタンス誤差は 5% 未満です)。

2. シールドおよび接地の設計ミス

- 標準ケースを超えるEMI: 360°終端シールドトランス(Pulse HX5008NLなど)が使用されておらず、二次側がYコンデンサを介して接地されていないため、コモンモードノイズがケーブルに結合します。

- 解決策:

- 完全にシールドされたトランス (金属ケース + 磁気的に包まれたワイヤ) を選択してください。

- グリッドトランスの二次側は、1nF Y コンデンサ (接地インピーダンス < 1Ω) を介して金属ケースに接続されています。

3. PoDL電源の設計上の欠陥

- 典型的な障害: PHY はクラス 4 PoDL (60W) をサポートしていますが、ネットワーク トランスには DC 絶縁機能が統合されていないため、電力とデータの競合が発生します。

- 準拠した設計:

- センタータップ付きの変圧器 (Bourns SM453230 など) を使用し、タップに 100μF のエネルギー蓄積コンデンサを追加します。

- 電流クランプを使用して PoDL ライン電流を測定し、チップ制限を超えていないことを確認します (たとえば、60W は 50V で 1.2A に相当します)。

─────────────────

4. 配線設計の主な問題点とその対策

1. 差動配線の設計ミス

- インピーダンスの不一致:

- 現象: 差動ラインのインピーダンスが制御されていないため (目標 100Ω±10%)、信号の反射が発生します。

- 訂正:SI9000を使用して線幅・間隔を再計算し、「マイクロストリップライン+グランド銅箔」構造を採用しました。

- 長さが等しくない:

- 標準: 差動ペア内の長さの誤差は 5mm 以内、外部グループ間の誤差は 25mm 以内です。

- ツール: Altium などの PCB 設計ソフトウェアで xSignals などの長い機能を有効にします。

2. デカップリングコンデンサのレイアウトミス

- 例: PHY 電源ピン近くの 0.1μF コンデンサ間の距離が 5mm より大きく、高周波ノイズが信号ラインに結合します。

- ルール:

- 各電源ピンに 0.1μF+1μF コンデンサを配置します (間隔 ≤2mm)。

- 低 ESR セラミック コンデンサ (X7R/X5R 材料など) を使用してください。

3. 分離ゾーンの設計上の欠陥

- 高電圧破壊のリスク: PHY 側 (DGND) とネットワーク トランス絶縁側 (PGND) が十分な沿面距離を維持していません。

- 安全要件:

- 一次/二次絶縁電圧 ≥1500Vrms (産業用) または 2500Vrms (自動車用)。

- PCB 上の分離領域の幅は 3 mm 以上 (強化絶縁)、漏れを防ぐために溝が設けられています。

─────────────────

V. 実戦事例:基準を超えるEMCと通信断続の総合障害

1. 故障現象

- EMC テストで、産業用 PLC モジュールが CE RE 制限を超え (120MHz 周波数帯域が制限を超え)、通信が断続的になりました。

2. デザインチェック

- PHY の選択: ADI ADIN1300 (工業用グレード、10/100Mbps をサポート)。

- ネットワークトランスモデル:HX5008NL(絶縁電圧2500Vrms)。

- 配線の問題:

- 差動線路長の差は12mm(標準>5mm)で、コモンモードチョークは追加されていません。

- グリッド変圧器の二次側が接地されておらず、電源デカップリング コンデンサがありません。

3. 是正措置

- ルーティングの最適化: 差動ラインを再レイアウトし (長さの差を 3 mm に縮小)、コモンモード フィルター (Murata DLW43SH101XK2) を追加します。

- 接地の強化: トランスの二次側の金属ケースに 1nF Y コンデンサを追加します。

- 電源フィルタリング: 100MHz フェライト ビーズ (TDK MMZ1608S102A) が PHY の 3.3V 電源入力に直列に接続されています。

4. テスト結果

- EMC 放射値は 15dB 低下し、通信ビット誤り率は 1e-5 から <1e-8 に低下しました。

─────────────────

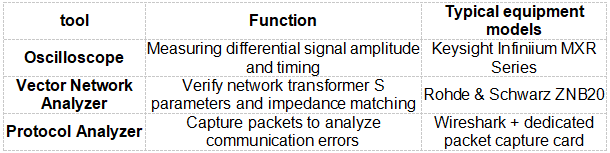

VI.設計検証およびデバッグツールボックス

1. ハードウェアテストツール

2. デバッグチェックリスト

- [ ] PHY レジスタは正しく構成されています (速度、デュプレックス モード、オートネゴシエーション)。

- [ ] ネットワークトランスの巻数比はプロトコルと一致します。

- [ ] 差動ラインインピーダンスは 100Ω±10% に準拠します。

- [ ] 電源デカップリング コンデンサのレイアウトは「近接原理」に準拠しています。

- [ ] グリッドトランスの二次側は Y コンデンサを介して接地されます。

─────────────────

PHY とネットワーク トランスの設計上の欠陥を正確に特定することで、イーサネット通信の異常を体系的に解決できます。ハードウェア エンジニアは、ソースでの通信リスクを回避するために、選択フェーズでパラメータを厳密に照合し、レイアウトに高速設計ルールを実装する必要があります。

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy