Chiplan とネットワーク変圧器の選択

Chiplan とネットワーク変圧器の選択

以下は、容量性/誘導性チップ LAN と統合ネットワーク トランスのより包括的な技術比較と設計分析です。内容は初期バージョンよりも約 2 倍深くなり、デバイスの内部構造分析、より実践的な設計課題の説明、業界応用技術の事例が追加されました。

─────────────────

パート 1: 容量性チップ LAN と統合ネットワークトランス -原理から実装までの体系的な分析

1. デバイスの構造と物理原理

容量性チップLAN:

- アーキテクチャの分解:

- 内部に集積された高圧セラミックコンデンサ(耐電圧1-2kV)が絶縁層として機能し、差動信号伝送ネットワークが両側に接続されています。

- ESD保護ダイオードとマイクロコモンモードインダクタが付属しており、スパイクとEMIを抑制します。

- 一般的なパッケージ: 0402/0603 チップ パッケージ、フル SMD 設計、磁気コアなし。

- 信号経路モデル:

- 高周波に対しては低いインピーダンスを示し、信号は通過しますが、DC パスはコンデンサによってブロックされます。

- 寄生インダクタンス (約 1-2nH) と分布容量 (0.5-1pF) は、10G を超える信号の減衰に直接影響します。

統合ネットワークトランス:

- アーキテクチャの分解:

- 磁気絶縁コア: フェライト磁気トロイドまたは平面トランス構造、一次巻線と二次巻線の比 1:1 (またはカスタマイズ)。

- 周辺回路: コモンモードインピーダンスのバランスをとるためのチップRCネットワークを内蔵しており、一部のモジュールにはコモンモードチョーク(CMC)が組み込まれています。

- パッケージ: 金属シールド付きの DIP/SMD モジュール (サイズ 6x6mm ~ 15x15mm)。

- 磁気結合効率:

- コア材料の初透磁率 (μi) と飽和磁束密度 (Bs) によって、帯域幅と電力処理能力が決まります。

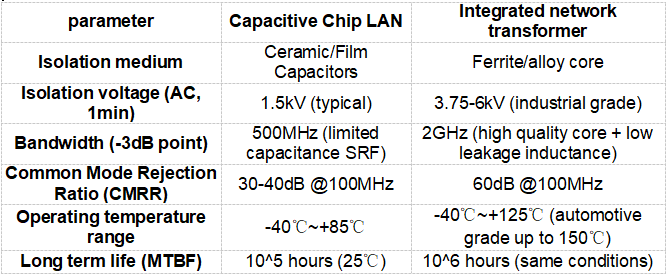

重要なパラメータの比較: コンデンサタイプとトランスタイプ

─────────────────

2. ハードウェア設計の深い課題と解決策

(1) 容量性チップ LAN 設計のリスク

- コンデンサ耐圧劣化:

- 高周波および高電圧 (PoE アプリケーションなど) で充放電を繰り返すと、コンデンサの誘電体が劣化し、漏れ電流が増加します。

- 対策: X7R/X8R などの安定性の高いセラミック コンデンサを選択し、20% の電圧マージンを確保してください。

- 高周波損失制御:

- 信号周波数が >1GHz の場合、コンデンサの自己共振周波数 (SRF) が有効帯域幅を制限します。

- 対策: PHY からコンデンサまでの配線長を短くし (<5mm)、ビアと直角ターンを無効にします。

(2) 統合ネットワーク変圧器の設計リスク

- 磁気飽和の問題:

- PoE++ (90W) などの高電力シナリオでは、大電流によりコアの飽和と損失の急増が発生します。

- 対策: Bs 値の高いセンダストまたはナノ結晶コアを選択し、エアギャップ (犠牲インダクタンス) を増やします。

- 高周波放射干渉:

- シールドされていない変圧器は GHz 帯域の放射線源となり、RF 回路 (Wi-Fi/BT モジュールなど) に影響を与えます。

- 対策:モジュール筐体を接地し、周囲に磁気吸収材(フェライトシート等)を配置してください。

─────────────────

3. アプリケーションシナリオの技術適応と代表的な事例

(1) 容量チップLANの柔軟な活用

- 高速充電とデータ送信の 2 つが 1 つ (USB PD + イーサネット):

- USB Type-C ドッキング ステーションでは、容量性 LAN を使用して、100W の電力供給をサポートしながらスペースを節約します。

- 設計の難しさ: 容量結合ノイズを防ぐために、PD プロトコル通信 (CC ライン) と差動信号を厳密に分離する必要があります。

- 産業用 IoT 低電力センサー ネットワーク:

- RS-485 to Ethernet ゲートウェイでは、コンデンサ絶縁が基本 2kV 耐電圧を満たしており、-40℃ の低温起動時にコア ヒステリシスがありません。

(2) 統合変圧器のハイエンドアプリケーション

- 800G 光モジュール SerDes インターフェイス絶縁:

- ウルトラワイドバンド (56G PAM4 をサポート) トランスを使用し、リニア ドライバーと組み合わせて損失を補います。

- SI 検証: TDR (タイム ドメイン反射率計) を使用して、インピーダンス マッチングと PCB 配線誤差が ±5% 以内であることを確認します。

- 電気自動車用のギガビット イーサネット バックボーン:

- コアとコイルの機械的強化設計、エポキシ樹脂ポッティングにより、振動や温度衝撃による破損を防ぎます。

─────────────────

パート 2: インダクティブ チップ LAN と統合ネットワーク トランス -高周波性能と信頼性における画期的な進歩

1. インダクティブチップLANの技術革新

(1) 磁気集積と半導体技術の融合

- 3D 積層インダクタ技術:

- TSV (シリコン貫通ビア) を使用してシリコン基板上にスパイラルインダクターを製造し、Q 値を 30% 向上させ、10GHz の超広帯域をサポートします。

- 代表的なメーカー: TDK の MLP シリーズ (Multi-Layer Pieced Inductor)。

- 磁気および電気複合絶縁:

- 誘導絶縁 + 容量結合のデュアルパス、冗長設計により、EMC レベルが向上します (CISPR 32 クラス B を満たすなど)。

(2) 誘導変圧器と従来の変圧器の性能限界

─────────────────

2. ハードウェア設計における高周波トラップとクラッキング手法

(1) インダクティブチップLANの信号リンギング抑制

- 根本原因:

- 高速信号エッジ (<100ps) は LC 共振を引き起こし、リンギングによりビット誤り率 (BER) が増加します。

- 対策:

- ドライバーのインピーダンスと一致させるために、PHY 側に 22Ω の抵抗 (または調整可能な終端ネットワーク) を直列に追加します。

- PCB スタックの最適化: 基準面は完全であり (分割を回避)、信号層と GND 層の間の間隔は <4mil です。

(2) 集積トランスの多ポートクロストーク制御

- 根本原因:

- スイッチ内のマルチポートトランスの磁界結合は、遠端クロストーク(FEXT)を悪化させる。

- 対策:

- モジュール間隔は10mm以上で、信号層の間にシールドされたグランドプレーンが挿入されています(ストリップライン構造)。

- シリアル ポートは千鳥状のレイアウトで配置されており、対称的な結合が崩れています。

─────────────────

3. 業界の最先端のアプリケーションと技術トレンド

(1) インダクティブチップLANのSiP統合

- 異種統合のケース:

- Intel「イーサネット SiP」: PHY チップ、インダクタ絶縁、TVS が 2.5Gbps の速度で 5x5mm パッケージに統合されています。

- 利点: PCB 面積が 60% 削減され、歩留まりが 99.8% に向上します (従来のモジュールは 97%)。

(2) 光磁気ハイブリッドアイソレーション技術

- テクニカルルート:

- トランス磁気回路にはVCSEL(Vertical Cavity Surface Laser)とフォトダイオードが埋め込まれており、磁気三重アイソレーションを実現しています。

- 30kVを超える電圧に耐え、UHV変電所監視システムで使用されています。

(3) 量子ドット磁心の研究開発

- イノベーション:

- 量子ドット磁性材料は高周波損失を 50% 削減し、1THz テラヘルツ通信のプロトタイプをサポートします。

- 考えられるシナリオ: 6G ワイヤレス バックホール ネットワーク、高精度レーダー干渉分離。

─────────────────

4. エンジニア選択決定ツリー

ステップ 1: 要件に優先順位を付ける

- 絶縁耐圧 > 3kV? → 変圧器を選択してください

- スペースコストを重視しますか? → 静電容量式を選択してください

- レート > 10Gbps? → トランスまたは高度なインダクターを選択してください

- 自動車-グレード認証が必要ですか? → AEC-Q200 トランスを選択してください

ステップ 2: サプライチェーンの安定性を確認する

- 容量性チップ LAN: 台湾メーカー (Yageo/Walsin) の供給サイクルは 8 週間であり、国内代替品 (Fenghua) の歩留まりを改善する必要があります。

- 統合トランス: 日本の TDK/村田製作所の納期は 12 週間で、国内の代替マグネトロン テクノロジーは長期的な信頼性を評価する必要があります。

ステップ 3: 予備調査およびテスト プロジェクト

- 必須項目:絶縁耐圧試験、TDRインピーダンス検証、サーマルサイクル(-55℃~+125℃ 1000回)

- オプション項目: HBM ESD 試験、塩水噴霧腐食試験 (海洋機器)、ランダム振動解析 (車両搭載)。

─────────────────

要約する

容量性/誘導性チップ LAN と統合ネットワークトランスには、それぞれ独自の技術的利点があります。

- 小型化とコスト: コンデンサ/インダクタ チップ LAN は家電製品と軽量 IoT の主流を占めています。

- 極めて高い信頼性とパフォーマンス: 統合変圧器は、依然として産業、自動車、軍事用途に最適な選択肢です。

- 将来の戦場: 3D 磁気統合、量子磁気コア、および磁気/光ハイブリッド絶縁テクノロジーは、業界の状況を再構築します。

設計のモットー: 「絶縁レベルと信号の完全性が第一原則であり、他のすべてはトレードオフです。」

共有する

関連リンク

あなたも好きかもしれません

前の記事

次の記事

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

Subscribe

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy