チプランおよびネットワークトランスの選択

チプランおよびネットワークトランスの選択

以下は、容量性/誘導チップLANおよび統合ネットワークトランスのより包括的な技術比較と設計分析です。コンテンツは、初期バージョンの約2倍の深さで、デバイス内部構造分析、より実用的な設計チャレンジの説明、業界アプリケーションテクノロジーのケースを追加します。

─~~~……七面、そして七面大時 - そして七度節七ome-七面

パート1:静電容量チップLAN対統合ネットワークトランス原則から実装までの体系的な分析

1。デバイスの構造と物理的原理

容量性チップlan:

- アーキテクチャ分解:

- 内部統合された高-電圧セラミックコンデンサ(耐用電圧1 - 2kV)は、両側に接続された差-モード信号伝送ネットワークを備えた分離層として機能します。

- ESD保護ダイオードとマイクロコモンモードインダクタが付属して、スパイクとEMIを抑制します。

- 典型的なパッケージ:0402/0603チップパッケージ、完全なSMDデザイン、磁気コアなし。

- 信号パスモデル:

- 高周波数に低いインピーダンスを示し、信号を通過させますが、DCパスはコンデンサによってブロックされます。

- 寄生インダクタンス(約1 - 2NH)および分布容量(0.5 - 1PF)は、10gを超える信号の減衰に直接影響します。

統合ネットワークトランス

- アーキテクチャ分解:

- 磁気分離コア:フェライト磁気トロイドまたは平面変圧器構造、一次対二次巻線比1:1(またはカスタマイズ)。

- 周辺回路:ビルド-チップRCネットワークで、共通モードのインピーダンスのバランスをとるために、一部のモジュールは共通モードチョーク(CMC)を統合します。

- パッケージ:金属シールド付きのDIP/SMDモジュール(サイズ6x6mmから15x15mm)。

- 磁気結合効率:

- コア材料の初期透過性(μI)と飽和フラックス密度(BS)は、帯域幅と電力処理機能を決定します。

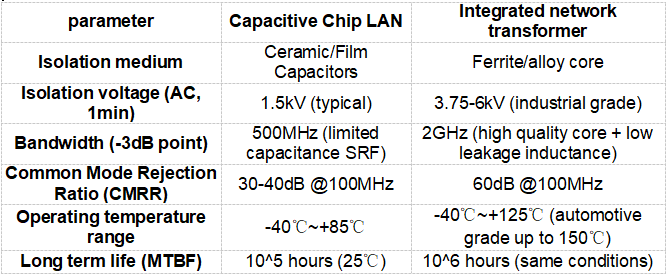

キーパラメーターの比較:コンデンサタイプ対トランスタイプ

─~~~……七面、そして七面大時 - そして七度節七ome-七面

2。ハードウェア設計のための深い課題とソリューション

(1)容量性チップLANデザインのリスク

- 電圧の分解に耐えるコンデンサ:

- 高周波と高電圧(POEアプリケーションなど)の繰り返し充電と放電により、コンデンサ誘電体の老化と漏れ電流が増加します。

- 対策:X7R/X8Rなどの安定性セラミックコンデンサを選択し、20%の電圧マージンを予約します。

- 高頻度損失制御:

- 信号周波数が> 1GHzの場合、コンデンサの自己-共振周波数(SRF)が有効帯域幅を制限します。

- 対策:Phyからコンデンサ(<5mm)までのトレースの長さを短くし、バイアスを無効にし、右角度ターンを無効にします。

(2)統合ネットワークトランスのリスクを設計します

- 磁気飽和問題:

- POE ++(90W)などの高電力シナリオでは、大きな電流がコアの飽和と急増する損失を引き起こします。

- 対策:BS値が高いSundustまたはナノ結晶コアを選択し、エアギャップを増加させます(犠牲インダクタンス)。

- 高周波放射干渉:

- シールドされていない変圧器は、GHZバンドの放射源になり、RF回路(Wi - Fi/BTモジュールなど)に影響します。

- 対策:モジュールのハウジングを接地し、その周りに磁気吸収材料(フェライトシートなど)を配置します。

─~~~……七面、そして七面大時 - そして七度節七ome-七面

3。アプリケーションシナリオテクノロジー適応と典型的なケース

(1)静電容量チップLANの柔軟な応用

- 高速充電とデータ送信2 - in - one(USB PD +イーサネット):

- USBタイプ- Cドッキングステーションでは、静電容量性LANを使用して、100Wの電力供給をサポートしながらスペースを節約します。

- 設計の難易度:容量性結合ノイズを防ぐために、PDプロトコル通信(CCライン)と差動信号は厳密に分離する必要があります。

- Industrial IoT Low -パワーセンサーネットワーク:

- Rs - 485からEthernet Gatewayへでは、コンデンサの分離が基本的な2kV耐音電圧を満たしており、- 40°低温起動のコアヒステリシスはありません。

(2)高-統合変圧器のエンドアプリケーション

- 800g光学モジュールSerdesインターフェイス分離:

- ウルトラ-ワイドバンド(56G PAM4)変圧器を使用し、それらを線形ドライバーと組み合わせて損失を補正します。

- SI検証:TDR(時間ドメイン反射計)を使用して、±5%以内のインピーダンスマッチングとPCBルーティングエラーを確保します。

- 電気自動車用のギガビットイーサネットバックボーン:

- コアとコイルの機械的強化設計、エポキシ樹脂ポッティングは、振動と温度ショックの下での破損を防ぎます。

─~~~……七面、そして七面大時 - そして七度節七ome-七面

パート2:帰納的チップLAN対統合ネットワークトランス高頻度のパフォーマンスと信頼性のブレークスルー

1。誘導チップlanの技術革新

(1)磁気統合と半導体技術の融合

- 3Dスタッキングインダクタテクノロジー:

- TSV(シリコン経由)を使用して、シリコン基板上でスパイラルインダクタを製造し、Q値を30%増加させ、10GHzウルトラ-ワイドバンドをサポートします。

- 典型的なメーカー:TDKのMLPシリーズ(マルチ-レイヤーピースインダクタ)。

- 磁気および電気の複合分離:

- 誘導分離 +容量性結合デュアルパス、冗長設計によりEMCレベルが向上します(CISPR 32クラスBを満たすなど)。

(2)誘導トランスと従来の変圧器の性能制限

─~~~……七面、そして七面大時 - そして七度節七ome-七面

2。高-ハードウェア設計における周波数トラップとクラッキング方法

(1)誘導チップLANの信号環抑制

- 根本的な原因:

- 高-速度信号エッジ(<100ps)トリガーLC共鳴を引き起こすと、リンギングによりビットエラー率(BER)が増加します。

- 対策:

- ドライバーのインピーダンスに合わせて、Phy側の22Ω抵抗(または調整可能な終端ネットワーク)を直列に追加します。

- PCBスタック- UP最適化:参照平面は完全です(クロス-セグメンテーションを避けます)、信号層とGND層の間の間隔は<4milです。

(2)統合変圧器のマルチ-ポートクロストーク制御

- 根本的な原因:

- スイッチ中のマルチ-ポート変圧器の磁場結合は、はるかに劣化します-エンドクロストーク(FEXT)。

- 対策:

- モジュール間隔は10mm以上で、シールドされたグランドプレーンが信号層(ストリップライン構造)の間に挿入されます。

- シリアルポートは、驚異的なレイアウトで配置され、対称的なカップリングを破壊します。

─~~~……七面、そして七面大時 - そして七度節七ome-七面

3。業界の切断-エッジアプリケーションとテクノロジーの傾向

(1)誘導チップLANのSIP統合

- 不均一な統合ケース:

- Intelの「イーサネットSIP」:PHYチップ、インダクタ分離、およびテレビは、2.5Gbpsのレートの5x5mmパッケージに統合されています。

- 利点:PCB面積を60%削減し、収率を99.8%に増やします(従来のモジュール97%)。

(2)Magneto -光学ハイブリッド分離技術

- 技術的なルート:

- VCSEL(垂直キャビティ表面レーザー)とフォトダイオードは、変圧器磁気回路に埋め込まれ、電気-光学トリプル分離を実現します。

- 30kVを超える耐性電圧は、UHV変電所監視システムで使用されています。

(3)量子ドット磁気コアの研究開発

- 革新:

- 量子ドット-ドープされた磁気材料は、高い-周波数損失を50%減少させ、1THZ Terahertz通信プロトタイプをサポートします。

- 潜在的なシナリオ:6Gワイヤレスバックホールネットワーク、高-精密レーダー干渉分離。

─~~~……七面、そして七面大時 - そして七度節七ome-七面

4.エンジニア選択決定ツリー

ステップ1:要件を優先します

- 分離は電圧> 3kVに耐えますか? →トランスを選択します

- スペースコストに敏感ですか? →容量性を選択します

- レート> 10gbps? →トランスまたは高度なインダクタを選択します

- 自動車-グレード認定が必要ですか? →AEC - Q200トランスを選択します

ステップ2:サプライチェーンの安定性を確認します

- 容量性チップLAN:台湾の製造業者(Yageo/Walsin)の供給サイクルは8週間であり、国内の代替品(Fenghua)の収量を改善する必要があります。

- 統合された変圧器:日本のTDK/ムラタの送達時間は12週間であり、国内の代替マグネトロン技術は長期的な信頼性を評価する必要があります。

ステップ3:予備調査およびテストプロジェクト

- 必要なアイテム:分離耐電圧テスト、TDRインピーダンスの検証、熱サイクル(- 55℃〜+125℃1000回)

- オプションのアイテム:HBM ESDテスト、塩スプレー腐食試験(海上機器)、ランダム振動分析(車両-マウント)。

─~~~……七面、そして七面大時 - そして七度節七ome-七面

要約します

容量性/誘導チップLANと統合ネットワークトランスはそれぞれ独自の技術的利点があります。

- 小型化とコスト:コンデンサ/インダクタチップLANは、家電と軽量IoTを支配しています。

- 極度の信頼性とパフォーマンス:統合された変圧器は、産業、自動車、軍事アプリケーションに依然として最良の選択肢です。

- 将来の戦場:3D磁気統合、量子磁気コア、および磁気-光学ハイブリッド分離技術は、業界の景観を再構築します。

設計モットー:「分離レベルと信号の完全性が第一原則であり、他のすべては貿易です-オフです。」

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy