イーサネットPHYチップテクノロジーホワイトペーパー

グローバル市場規模

2023年:約12億米ドル(データソース:YoleDévelopement)2028予測:25億米ドル(CAGR 15.8%)成長ドライバー:データセンターのアップグレード(400G/800G PHY需要)自動インテリジェンス(車両あたりの物理学数は1 - 2から10+から10歳以上に増加しました)

地域市場の分布

北米:40%(データセンターと自動車エレクトロニクスが駆動)アジア太平洋:35%(中国は主要な成長ポール、5Gベースステーション、電気自動車需要)ヨーロッパ:20%(産業4.0および自動車産業チェーン成熟)

市場競争パターン

北米:40%(データセンターと自動車エレクトロニクスが駆動)アジア太平洋:35%(中国は主要な成長ポール、5Gベースステーション、電気自動車需要)ヨーロッパ:20%(産業4.0および自動車産業チェーン成熟)

将来の傾向

1。テクノロジーの方向:

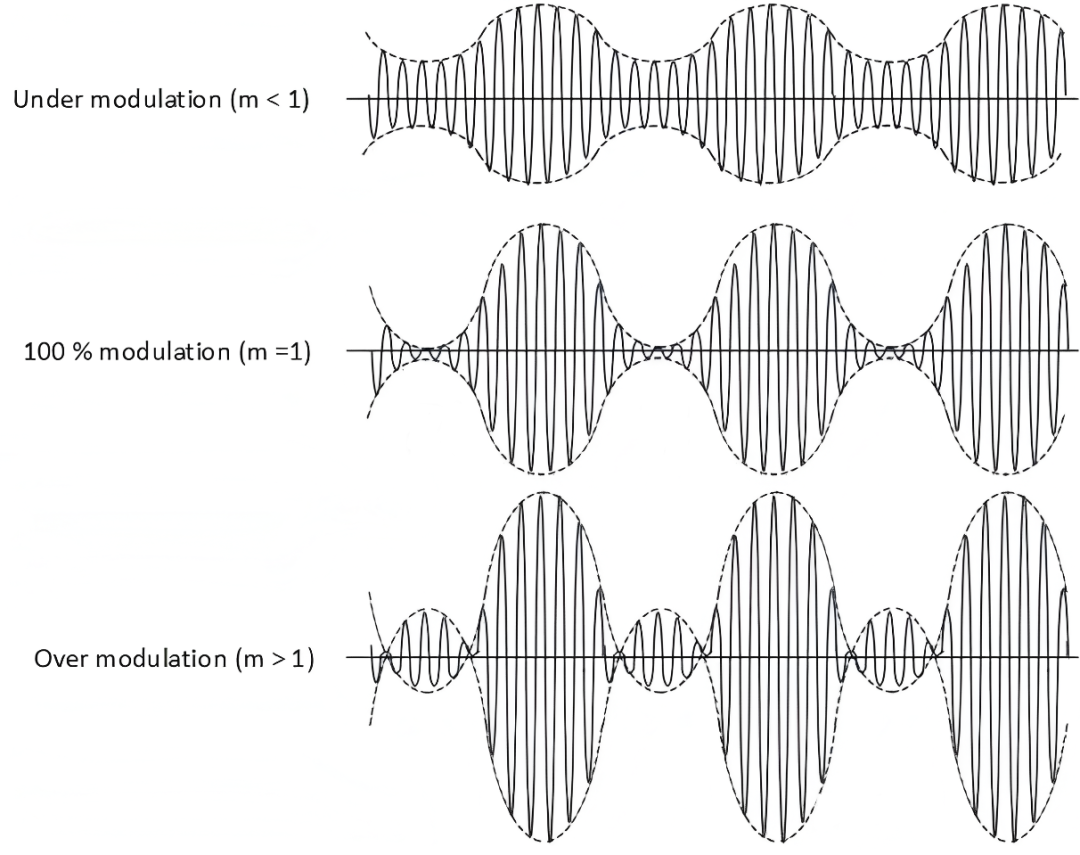

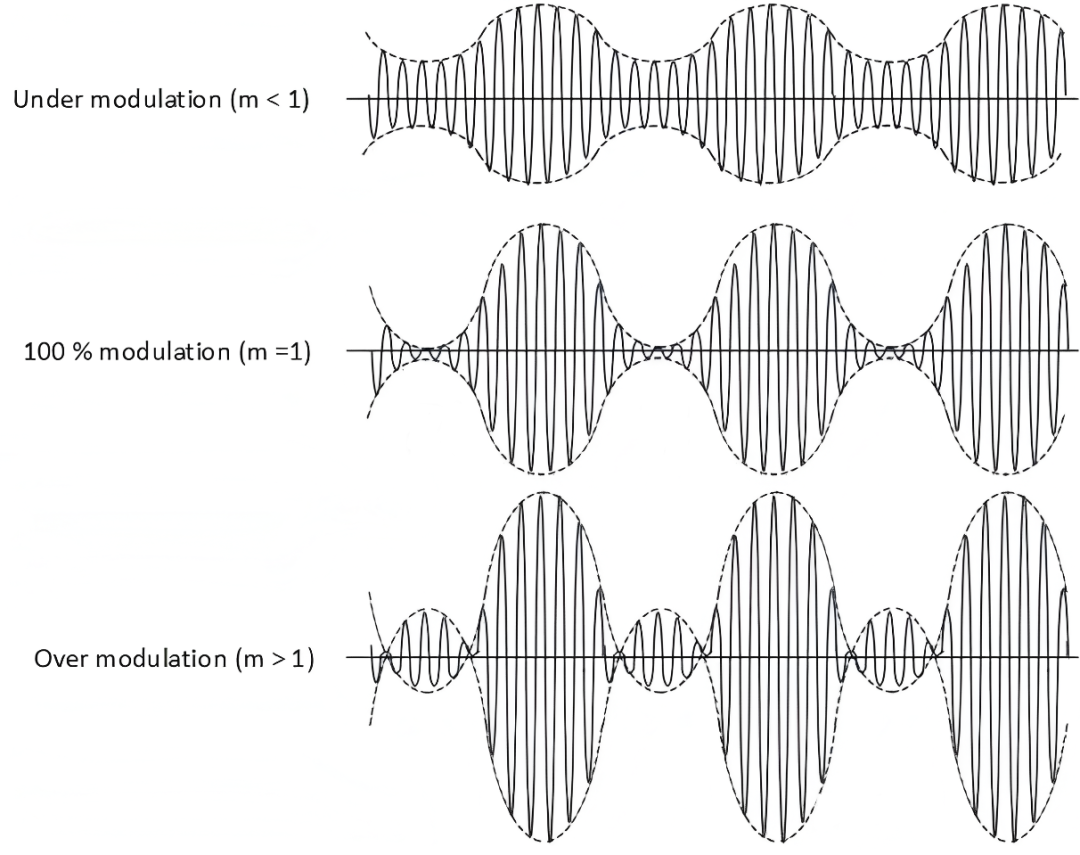

ウルトラ-高速:800g PHY(PAM4変調、シリコンフォトニクスの統合)低消費電力:3NMプロセスPHYチップ(電力消費量が50%削減)自動車グレード:10G PHYはL4/L5自律運転(2025年の大量生産)をサポートします。

2。サプライチェーンの変更:

米国は、中国への高等教育の輸出を制限し、国内代替のプロセスを加速しています。 TSMC/Samsungは、3NM Phy Foundryを展開して、最高-エンドマーケットを競い合います。

マックと物理メディア(銅ケーブル/光ファイバー)を接続して、安定したネットワーク伝送を確保する

1。信号調整

MACレイヤーによって送信された並列データをシリアルビットストリームに変換し、受信したアナログ信号をサンプルおよびデコードしてデジタル信号に復元します。

2。データエンコード/デコード

長い距離ケーブルでの高-周波数信号の減衰を補償し、インター-シンボル干渉(ISI)を排除し、信号波形を復元します。

3。物理メディアインターフェイス

ツイストペア +光ファイバ +バックプレーン。 ESD保護と共通モードの抑制で構築されています。

4。電力管理と診断

アイドル状態の場合、未使用のトランシーバーチャネルを閉じ、低電力モードでは消費電力を70%削減できます。ケーブル開回路/短絡/インピーダンスの異常と読み取りリンクステータスを検出する機能があります。

5.リンク交渉はレートに適応します

FLP(高速リンクパルス)を介してピアデバイスと最適なレート(10/100/1000Mbps)を交渉し、再接続を迅速に確立します。

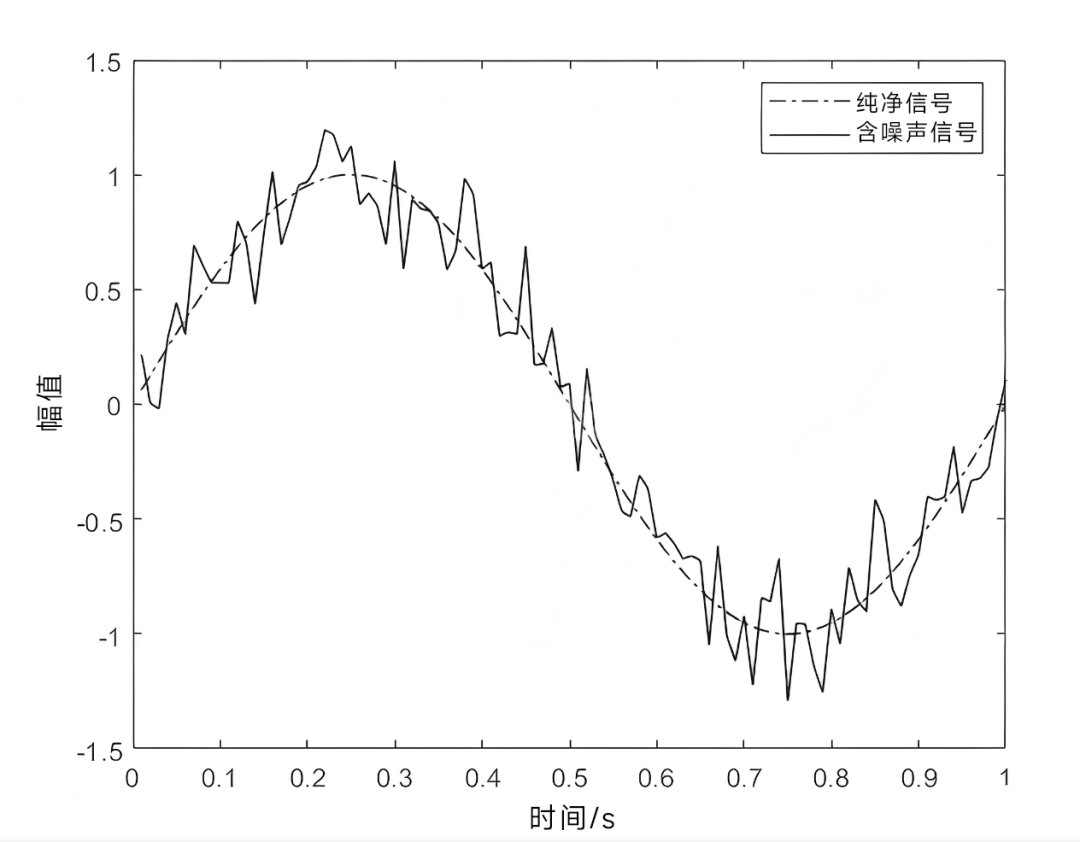

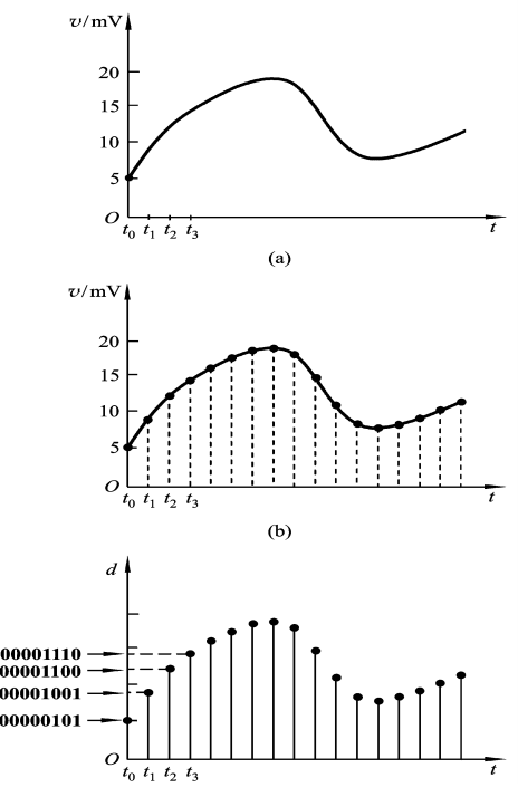

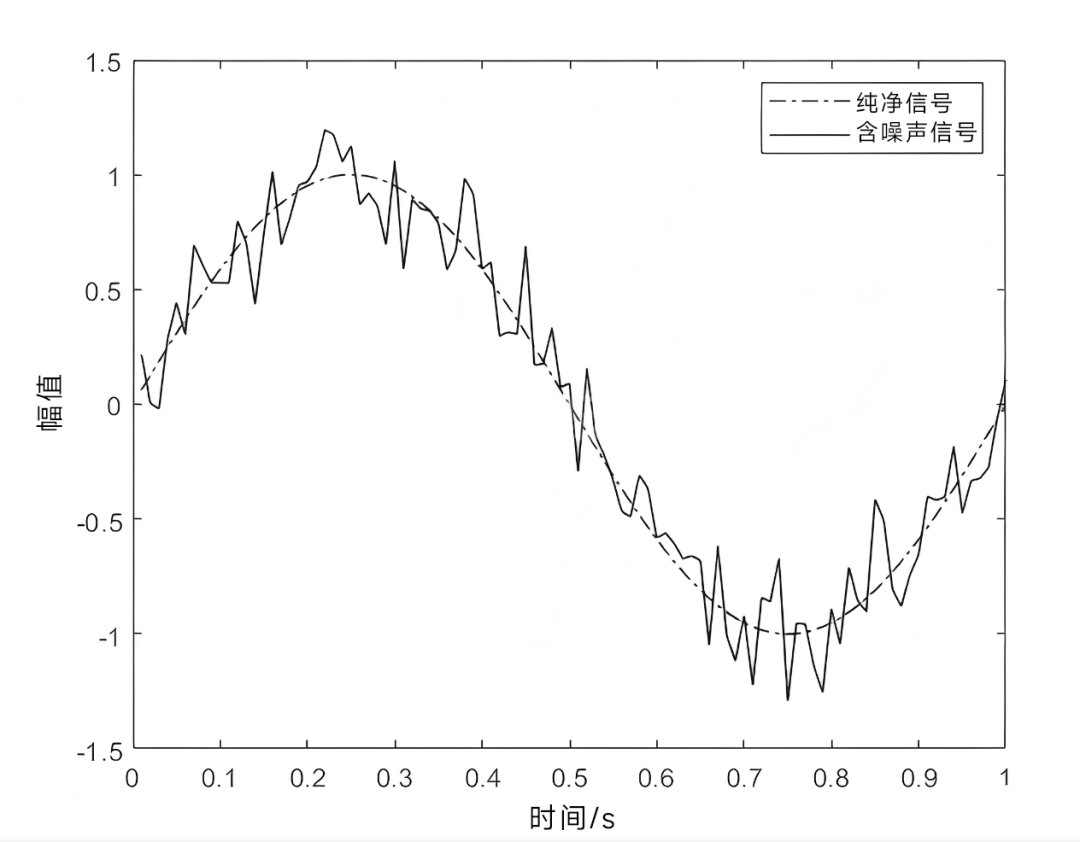

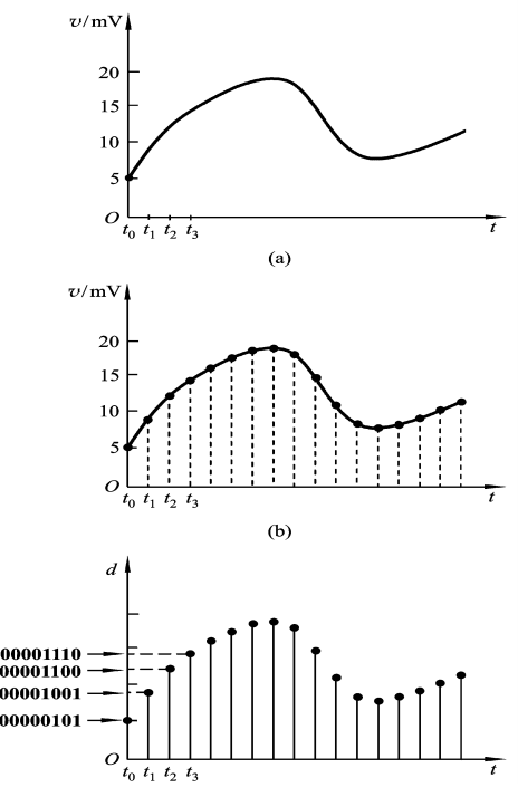

信号コンディショニング/データエンコードとデコード

1。信号条件付けの必要性

・信号振幅調整:シグナルの増幅イージー収集

2。信号コンディショニングプロセス(ほとんどの長い-距離通信に適用)

信号増幅->フィルタリング->信号変換->線形化->分離保護->変調と復調->レベル調整;

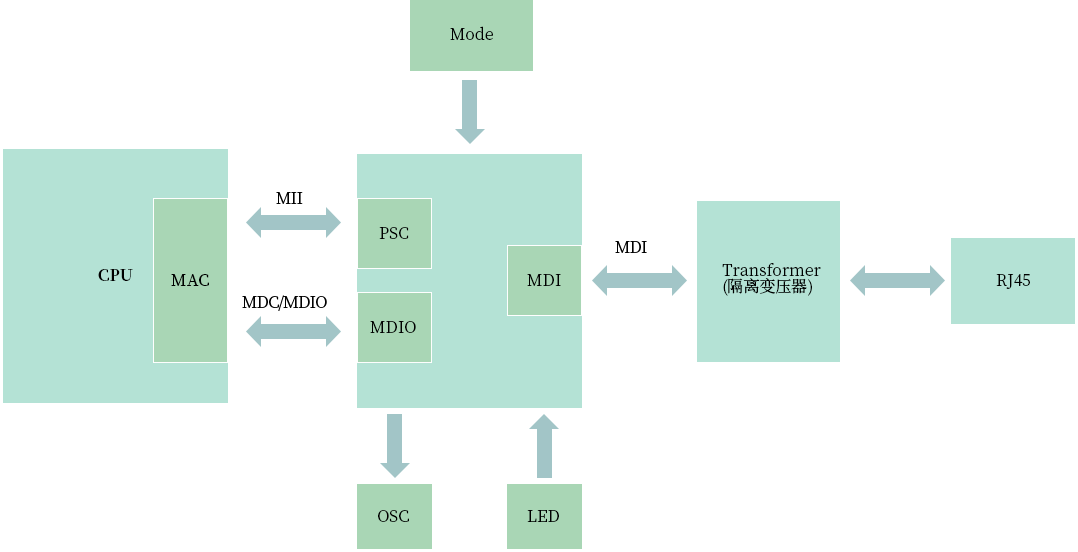

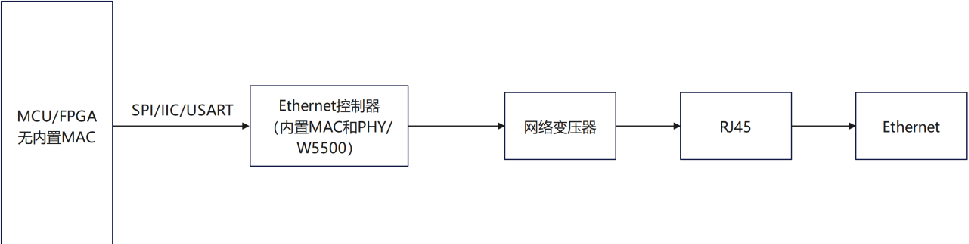

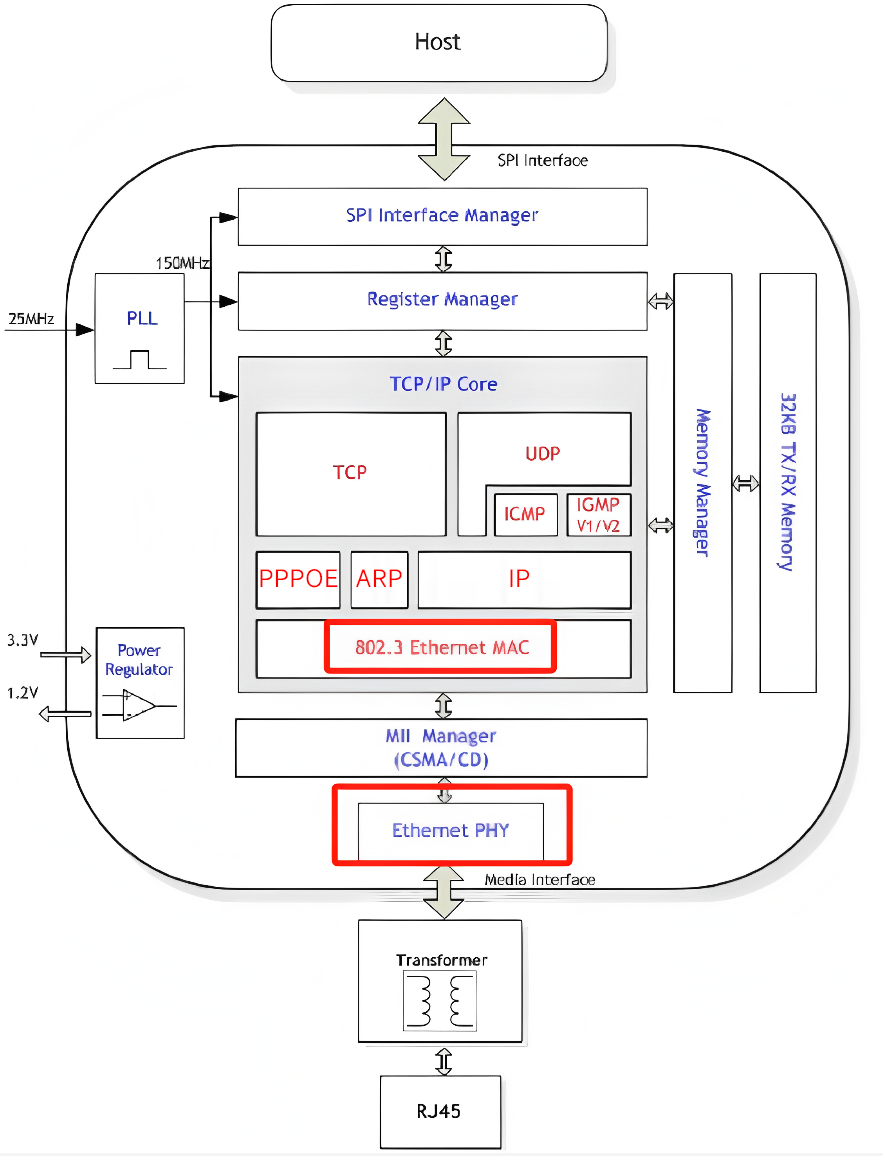

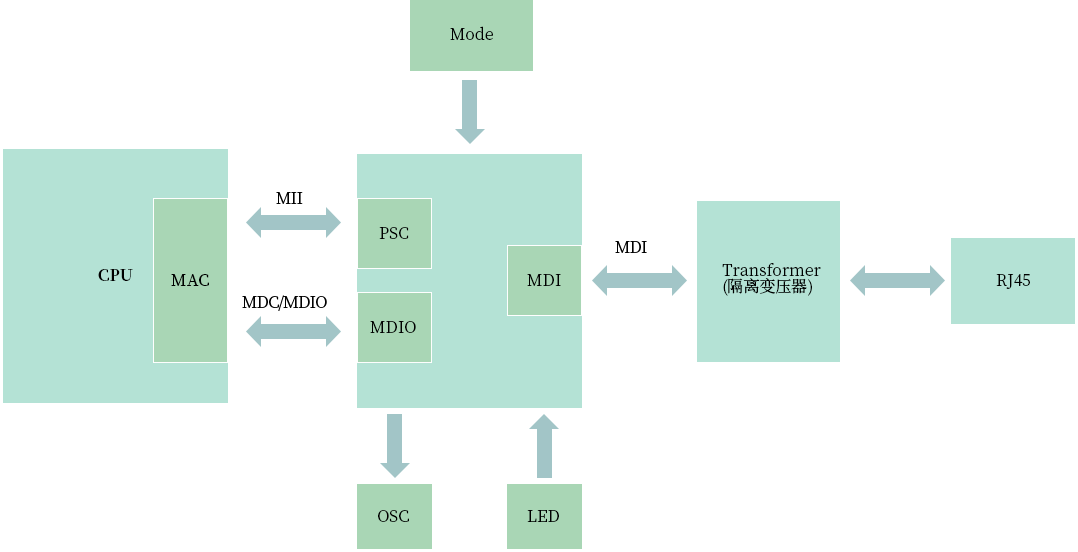

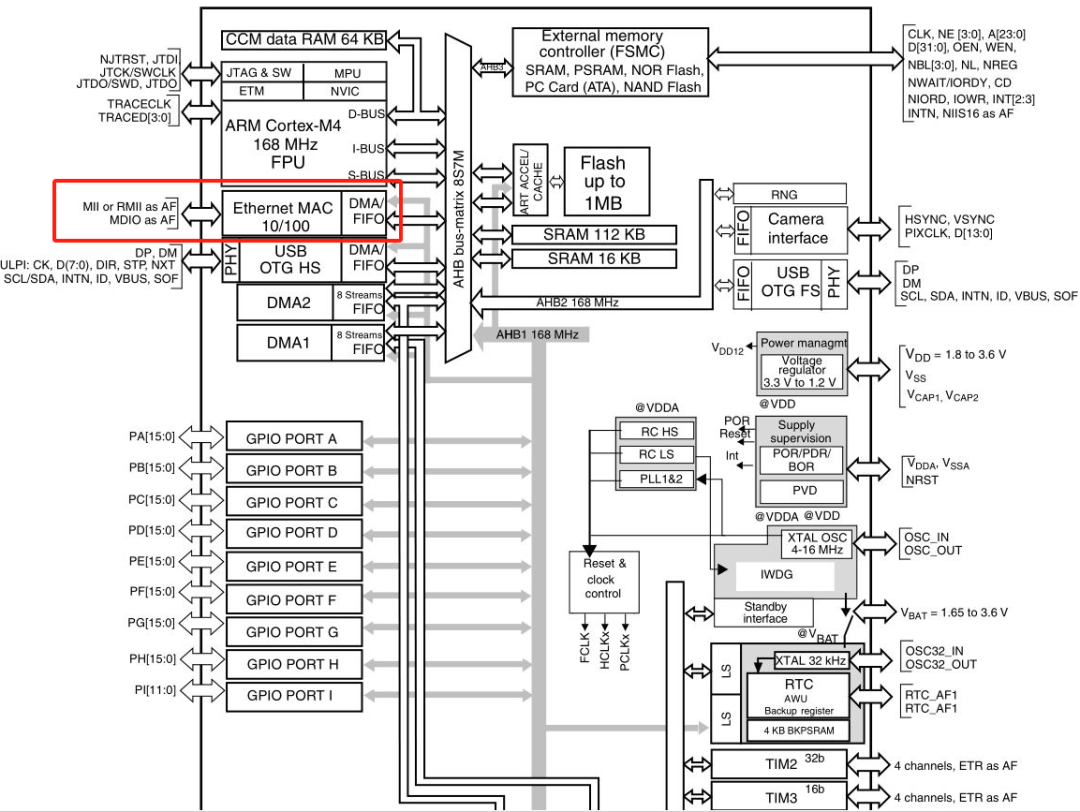

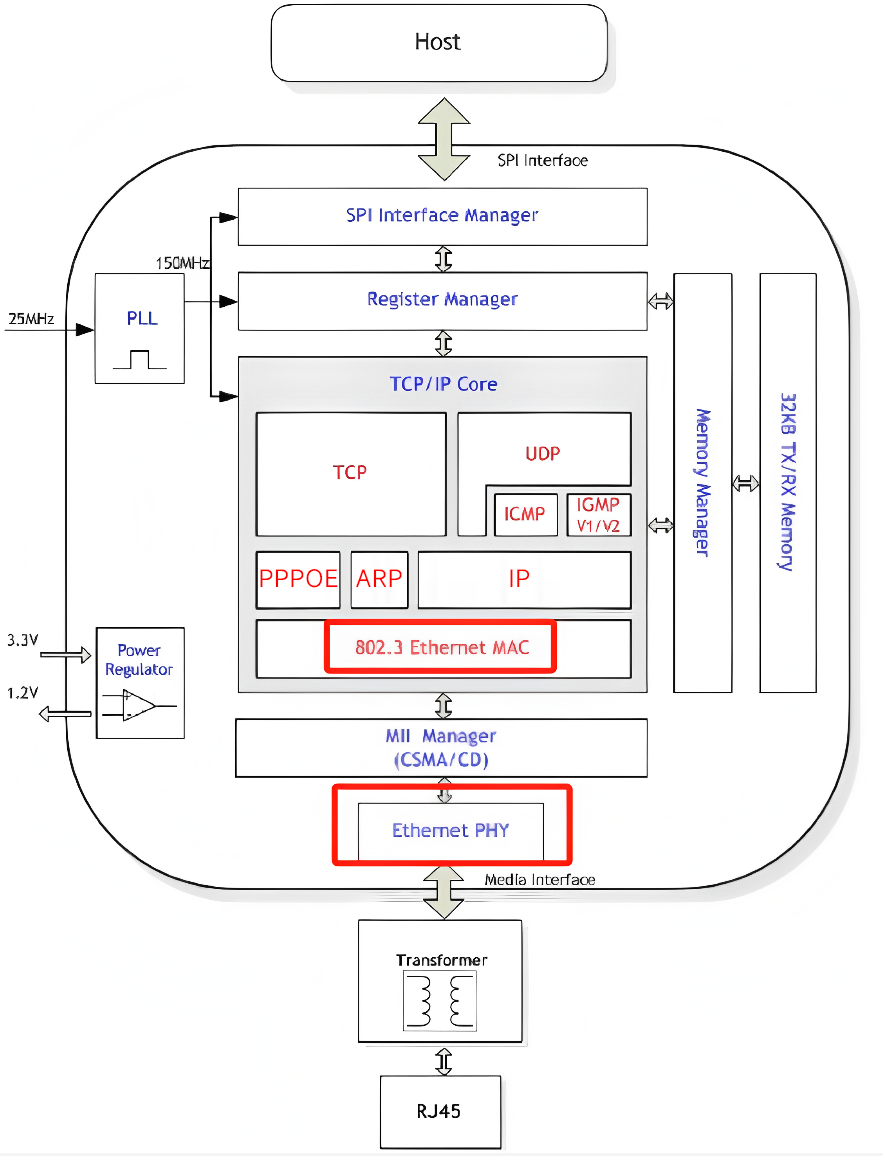

構造図

Phy Chip

PHY(物理層)チップは、物理層のコアコンポーネントであり、イーサネット信号の送信と受信を担当します。主な機能には次のものが含まれます。

•信号変換:デジタル信号をネットワークケーブル伝送(伝送)に適したアナログ信号に変換し、アナログ信号をデジタル信号(受信)に変換します。

•電気保護:ネットワーク変圧器を介して追加の電気分離を提供して、落雷や電磁干渉などの外部要因による損傷からPHYチップを保護します。

ネットワークトランス

•信号のカップリングと伝送:差動モードのカップリングを介して、PHYチップによる差動信号出力をネットワークケーブルのもう一方の端に強化および送信します。

•電気分離:PHYチップとネットワークケーブルの間のDCレベルの差を隔離して、異なるデバイス間の電圧の差がデバイスに損傷を与えるのを防ぎます。

•インピーダンスマッチング:信号の反射とビットエラーを減らすために、信号ソース、負荷、伝送ライン間のインピーダンスマッチングを確認します。

•電磁干渉抑制:共通モードのノイズを抑制し、共通モードチョーク(CMC)を介して電磁干渉を減らします。

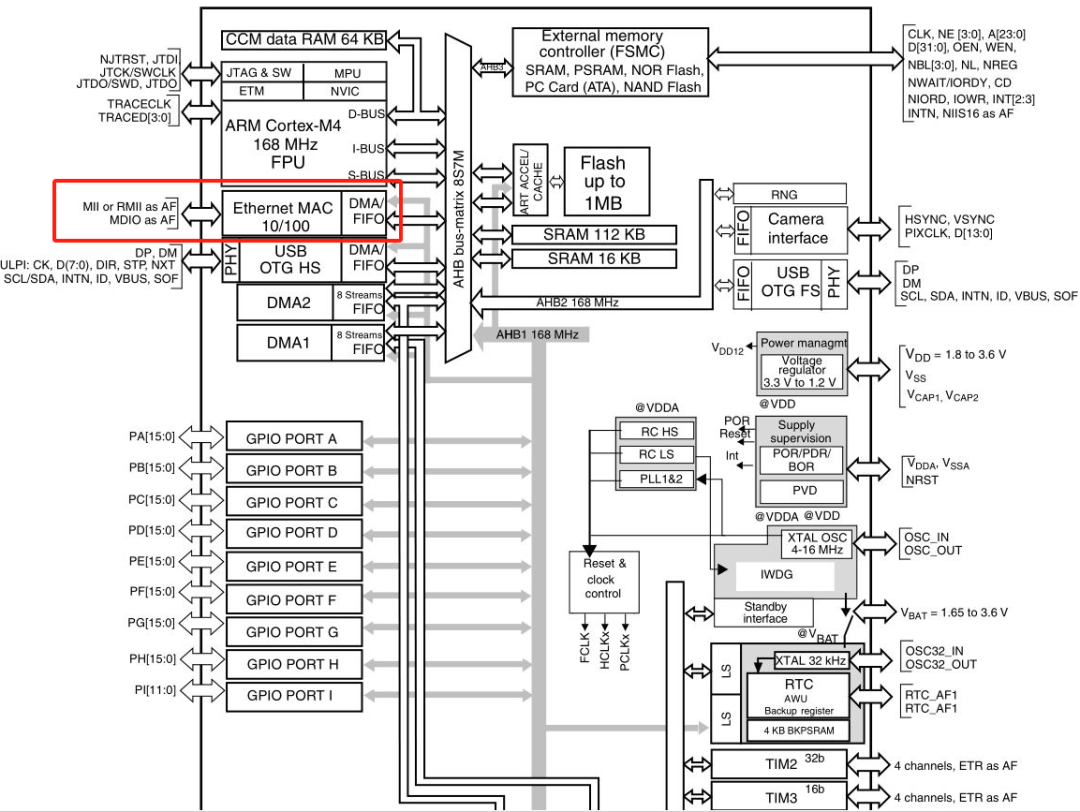

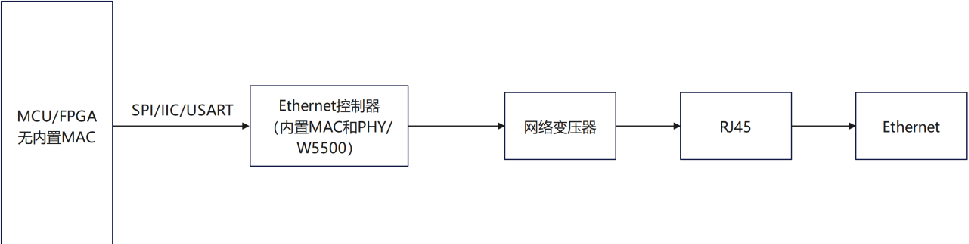

上記の3つの部分は、必ずしもすべて独立したチップではありません。主に次の状況があります。MacとPhyはCPU内に統合されていますが、これはより困難です。 MacはCPU内に統合されており、Phyは独立したチップを使用しています(主流のソリューション)。 MacとPhyはCPUに統合されておらず、MacとPhyは独立したチップまたは統合チップを使用します(高- end使用)。

パラメーター

1。レートサポート

•サポートレート範囲:PHYチップは、10 Mbps、100 Mbps、1 Gbps、10 Gbpsなど、ターゲットアプリケーションで必要なイーサネットレートをサポートする必要があります。

•アダプティブレートの交渉:サポートオート-ネゴシエーション関数。これは、ピアデバイスの機能に応じて、最高のレート(10/100/1000 Mbpsなど)およびデュプレックスモード(フル-デュプレックス/ハーフ-デュプレックス)を自動的に選択できます。

2。インターフェイス標準

Phyチップは、上部MACレイヤーと互換性がある必要があります。一般的なインターフェイスには以下が含まれます。

•MII:10/100 Mbpsイーサネットに適用されます。

•RMII:10/100 Mbpsに適した、ピンが少ないMIIの簡易バージョン。

•GMII:1 Gbpsレートをサポートします。

•RGMII:1 gbpsに適したピンを少なくしたGMIIの単純化バージョン。

•SGMII:シリアルインターフェイス、ピンが少ない1 Gbpsに適しています。

•物理媒体インターフェイス(MDI):ツイストペア(ベース- T)、ファイバー(ベース- X)、シングルツイストペア(ベース- T1)などのサポートされた物理メディアタイプ。

3。送信距離

•送信距離:アプリケーションの要件に応じて、必要な伝送距離をサポートするPhyチップを選択します。たとえば、1000base - T(Gigabit Ethernet)は最大100メートルまでのツイストペアトランスミッションをサポートしますが、ファイバーPhy(1000base - lxなど)はより長い距離をサポートできます。

4。消費電力

•消費電力レベル:低電力設計は、特に高密度デバイス(スイッチなど)やモバイルデバイスで、省エネと熱管理にとって重要です。たとえば、EEE(エネルギー効率の高いイーサネット)標準をサポートするPhyチップは、アイドル時に消費電力を削減できます。

•熱設計:特に高温環境または密度アプリケーションで、PHYチップの熱散逸要件を検討してください。

5。信頼性と安定性

•電気分離:電気的分離は、ネットワークトランスを介して達成され、落雷や電磁干渉などの外部要因による損傷からPhyチップを保護します。

•アンチ-干渉能力:PHYチップは、良好な電磁互換性(EMC)を持ち、産業環境での電磁干渉に耐えることができるはずです。たとえば、CISPR 32やIEC 61000 - 4 - 2などの標準に準拠する必要があります。

•動作温度範囲:産業-グレードのPhyチップは通常、厳しい環境に適応するために広い温度範囲(- 40°C85°Cなど)をサポートします。

6。特別な機能

•POEサポート:アプリケーションをイーサネットケーブル(IPカメラ、ワイヤレスアクセスポイントなど)で駆動する必要がある場合、POE(IEEE 80をサポートするチップを選択する必要があります。

•診断機能:ネットワークのメンテナンスとトラブルシューティングを容易にするために、リンクステータスの検出や信号品質モニタリングなどの機能をサポートします。 •セキュリティ機能:一部のアプリケーションでは、PHYチップが暗号化された通信や認証機能などのセキュリティ機能をサポートする必要がある場合があります。

アプリケーションシナリオ

(1)10/100Mbps Phy

アプリケーションシナリオ:産業制御:PLC、センサーネットワーク(Modbus TCPなど)スマートホーム:スマートソケット、低-電源IoTデバイス(Zigbeeゲートウェイなど)-ボード診断:OBD - IIインターフェイス(100ベース- T1)

(2)1Gbps Phy

アプリケーションシナリオ:コンシューマーエレクトロニクス:4Kテレビ、NASストレージ産業カメラ:マシンビジョン(リアル-タイムイメージ伝送)エンタープライズネットワーク:ギガビットスイッチ、ルーター

(3)2.5g/5g Phy(Multi - gigabit)

アプリケーションシナリオ:産業制御:PLC、センサーネットワーク(Modbus TCPなど)スマートホーム:スマートソケット、低-電源IoTデバイス(Zigbeeゲートウェイなど)-ボード診断:OBD - IIインターフェイス(100ベース- T1)

(4)10g/25g Phy

アプリケーションシナリオ:データセンター:サーバーの相互接続(SFP+/QSFP28)5Gベースステーション:Fronthaulネットワーク(25Gを超えるECPRI)ULTRA - HIGH -定義ビデオ生産:8Kビデオリアル-タイム伝達

(5)40g/100g以上

アプリケーションシナリオ:AI/スーパーコンピューティングクラスター:GPU/TPU相互接続(インフィニバンド交換)コアバックボーンネットワーク:メトロポリタンエリアネットワーク/インター-データセンター相互接続光学通信:CPRI/OBSAI FIBER FRONTHAUL

デザインの選択

(1)MII(メディア独立インターフェイス)

レート:10/100Mbpsピンの数:16+アプリケーションシナリオ:早期埋め込みシステム(ARM9産業コントロールボードなど)低い-複雑さの設計(外部Macコントローラーが必要)欠点:複雑な配線、RMIIに徐々に置き換えられました

(2)RMII(MIIの減少)

レート:10/100Mbpsピンの数:6(データ +クロック)アプリケーションシナリオ:コスト-敏感なデバイス(ホームルーターなど)スペース-制約付きデザイン(IoTモジュール)利点:単純化された配線、50MHzクロックのサポート

(3)rgmii(ギガビットMIIの削減)

レート:1Gbpsピンの数:12(デュアル-エッジサンプリング)アプリケーションシナリオ:ギガビットスイッチ、産業用ゲートウェイは100m/1gの柔軟な設計キーポイントと互換性がある必要があります:厳密なタイミング制御が必要です(±1NS偏差耐性)

(4)SGMII(シリアルギガビットMII)

レート:ピンの1g/2.5GbpsNumberの数:2(微分ペア)アプリケーションシナリオ:長距離ボード- - -ボード接続(SERDES経由)高- FPGAとPHYADVANTAGESの間の速度通信:強力な干渉、バックプレーン送信をサポート

(5)USXGMII(ウルトラスピードMII)

レート:ピンの10gbpsNumber:4(微分ペア)アプリケーションシナリオ:マルチ-レートスイッチ(10m/100m/1g/10gアダプティブ)データセンターリーフ-スパインアーキテクチャフィーチャー:低ジッタークロックが必要(<0.5ps RMS)

利点

適切な信頼性戦略は、オンデマンドでカスタマイズできます

製品の信頼性テストは、次の国際基準に厳密に準拠しています。

2023年:約12億米ドル(データソース:YoleDévelopement)2028予測:25億米ドル(CAGR 15.8%)成長ドライバー:データセンターのアップグレード(400G/800G PHY需要)自動インテリジェンス(車両あたりの物理学数は1 - 2から10+から10歳以上に増加しました)

地域市場の分布

北米:40%(データセンターと自動車エレクトロニクスが駆動)アジア太平洋:35%(中国は主要な成長ポール、5Gベースステーション、電気自動車需要)ヨーロッパ:20%(産業4.0および自動車産業チェーン成熟)

市場競争パターン

北米:40%(データセンターと自動車エレクトロニクスが駆動)アジア太平洋:35%(中国は主要な成長ポール、5Gベースステーション、電気自動車需要)ヨーロッパ:20%(産業4.0および自動車産業チェーン成熟)

将来の傾向

1。テクノロジーの方向:

ウルトラ-高速:800g PHY(PAM4変調、シリコンフォトニクスの統合)低消費電力:3NMプロセスPHYチップ(電力消費量が50%削減)自動車グレード:10G PHYはL4/L5自律運転(2025年の大量生産)をサポートします。

2。サプライチェーンの変更:

米国は、中国への高等教育の輸出を制限し、国内代替のプロセスを加速しています。 TSMC/Samsungは、3NM Phy Foundryを展開して、最高-エンドマーケットを競い合います。

製品機能

マックと物理メディア(銅ケーブル/光ファイバー)を接続して、安定したネットワーク伝送を確保する

1。信号調整

MACレイヤーによって送信された並列データをシリアルビットストリームに変換し、受信したアナログ信号をサンプルおよびデコードしてデジタル信号に復元します。

2。データエンコード/デコード

長い距離ケーブルでの高-周波数信号の減衰を補償し、インター-シンボル干渉(ISI)を排除し、信号波形を復元します。

3。物理メディアインターフェイス

ツイストペア +光ファイバ +バックプレーン。 ESD保護と共通モードの抑制で構築されています。

4。電力管理と診断

アイドル状態の場合、未使用のトランシーバーチャネルを閉じ、低電力モードでは消費電力を70%削減できます。ケーブル開回路/短絡/インピーダンスの異常と読み取りリンクステータスを検出する機能があります。

5.リンク交渉はレートに適応します

FLP(高速リンクパルス)を介してピアデバイスと最適なレート(10/100/1000Mbps)を交渉し、再接続を迅速に確立します。

信号コンディショニング/データエンコードとデコード

1。信号条件付けの必要性

・信号振幅調整:シグナルの増幅イージー収集

2。信号コンディショニングプロセス(ほとんどの長い-距離通信に適用)

信号増幅->フィルタリング->信号変換->線形化->分離保護->変調と復調->レベル調整;

構造図

Phy Chip

PHY(物理層)チップは、物理層のコアコンポーネントであり、イーサネット信号の送信と受信を担当します。主な機能には次のものが含まれます。

•信号変換:デジタル信号をネットワークケーブル伝送(伝送)に適したアナログ信号に変換し、アナログ信号をデジタル信号(受信)に変換します。

•電気保護:ネットワーク変圧器を介して追加の電気分離を提供して、落雷や電磁干渉などの外部要因による損傷からPHYチップを保護します。

ネットワークトランス

•信号のカップリングと伝送:差動モードのカップリングを介して、PHYチップによる差動信号出力をネットワークケーブルのもう一方の端に強化および送信します。

•電気分離:PHYチップとネットワークケーブルの間のDCレベルの差を隔離して、異なるデバイス間の電圧の差がデバイスに損傷を与えるのを防ぎます。

•インピーダンスマッチング:信号の反射とビットエラーを減らすために、信号ソース、負荷、伝送ライン間のインピーダンスマッチングを確認します。

•電磁干渉抑制:共通モードのノイズを抑制し、共通モードチョーク(CMC)を介して電磁干渉を減らします。

上記の3つの部分は、必ずしもすべて独立したチップではありません。主に次の状況があります。MacとPhyはCPU内に統合されていますが、これはより困難です。 MacはCPU内に統合されており、Phyは独立したチップを使用しています(主流のソリューション)。 MacとPhyはCPUに統合されておらず、MacとPhyは独立したチップまたは統合チップを使用します(高- end使用)。

パラメーター

1。レートサポート

•サポートレート範囲:PHYチップは、10 Mbps、100 Mbps、1 Gbps、10 Gbpsなど、ターゲットアプリケーションで必要なイーサネットレートをサポートする必要があります。

•アダプティブレートの交渉:サポートオート-ネゴシエーション関数。これは、ピアデバイスの機能に応じて、最高のレート(10/100/1000 Mbpsなど)およびデュプレックスモード(フル-デュプレックス/ハーフ-デュプレックス)を自動的に選択できます。

2。インターフェイス標準

Phyチップは、上部MACレイヤーと互換性がある必要があります。一般的なインターフェイスには以下が含まれます。

•MII:10/100 Mbpsイーサネットに適用されます。

•RMII:10/100 Mbpsに適した、ピンが少ないMIIの簡易バージョン。

•GMII:1 Gbpsレートをサポートします。

•RGMII:1 gbpsに適したピンを少なくしたGMIIの単純化バージョン。

•SGMII:シリアルインターフェイス、ピンが少ない1 Gbpsに適しています。

•物理媒体インターフェイス(MDI):ツイストペア(ベース- T)、ファイバー(ベース- X)、シングルツイストペア(ベース- T1)などのサポートされた物理メディアタイプ。

3。送信距離

•送信距離:アプリケーションの要件に応じて、必要な伝送距離をサポートするPhyチップを選択します。たとえば、1000base - T(Gigabit Ethernet)は最大100メートルまでのツイストペアトランスミッションをサポートしますが、ファイバーPhy(1000base - lxなど)はより長い距離をサポートできます。

4。消費電力

•消費電力レベル:低電力設計は、特に高密度デバイス(スイッチなど)やモバイルデバイスで、省エネと熱管理にとって重要です。たとえば、EEE(エネルギー効率の高いイーサネット)標準をサポートするPhyチップは、アイドル時に消費電力を削減できます。

•熱設計:特に高温環境または密度アプリケーションで、PHYチップの熱散逸要件を検討してください。

5。信頼性と安定性

•電気分離:電気的分離は、ネットワークトランスを介して達成され、落雷や電磁干渉などの外部要因による損傷からPhyチップを保護します。

•アンチ-干渉能力:PHYチップは、良好な電磁互換性(EMC)を持ち、産業環境での電磁干渉に耐えることができるはずです。たとえば、CISPR 32やIEC 61000 - 4 - 2などの標準に準拠する必要があります。

•動作温度範囲:産業-グレードのPhyチップは通常、厳しい環境に適応するために広い温度範囲(- 40°C85°Cなど)をサポートします。

6。特別な機能

•POEサポート:アプリケーションをイーサネットケーブル(IPカメラ、ワイヤレスアクセスポイントなど)で駆動する必要がある場合、POE(IEEE 80をサポートするチップを選択する必要があります。

•診断機能:ネットワークのメンテナンスとトラブルシューティングを容易にするために、リンクステータスの検出や信号品質モニタリングなどの機能をサポートします。 •セキュリティ機能:一部のアプリケーションでは、PHYチップが暗号化された通信や認証機能などのセキュリティ機能をサポートする必要がある場合があります。

アプリケーションシナリオ

(1)10/100Mbps Phy

アプリケーションシナリオ:産業制御:PLC、センサーネットワーク(Modbus TCPなど)スマートホーム:スマートソケット、低-電源IoTデバイス(Zigbeeゲートウェイなど)-ボード診断:OBD - IIインターフェイス(100ベース- T1)

(2)1Gbps Phy

アプリケーションシナリオ:コンシューマーエレクトロニクス:4Kテレビ、NASストレージ産業カメラ:マシンビジョン(リアル-タイムイメージ伝送)エンタープライズネットワーク:ギガビットスイッチ、ルーター

(3)2.5g/5g Phy(Multi - gigabit)

アプリケーションシナリオ:産業制御:PLC、センサーネットワーク(Modbus TCPなど)スマートホーム:スマートソケット、低-電源IoTデバイス(Zigbeeゲートウェイなど)-ボード診断:OBD - IIインターフェイス(100ベース- T1)

(4)10g/25g Phy

アプリケーションシナリオ:データセンター:サーバーの相互接続(SFP+/QSFP28)5Gベースステーション:Fronthaulネットワーク(25Gを超えるECPRI)ULTRA - HIGH -定義ビデオ生産:8Kビデオリアル-タイム伝達

(5)40g/100g以上

アプリケーションシナリオ:AI/スーパーコンピューティングクラスター:GPU/TPU相互接続(インフィニバンド交換)コアバックボーンネットワーク:メトロポリタンエリアネットワーク/インター-データセンター相互接続光学通信:CPRI/OBSAI FIBER FRONTHAUL

デザインの選択

(1)MII(メディア独立インターフェイス)

レート:10/100Mbpsピンの数:16+アプリケーションシナリオ:早期埋め込みシステム(ARM9産業コントロールボードなど)低い-複雑さの設計(外部Macコントローラーが必要)欠点:複雑な配線、RMIIに徐々に置き換えられました

(2)RMII(MIIの減少)

レート:10/100Mbpsピンの数:6(データ +クロック)アプリケーションシナリオ:コスト-敏感なデバイス(ホームルーターなど)スペース-制約付きデザイン(IoTモジュール)利点:単純化された配線、50MHzクロックのサポート

(3)rgmii(ギガビットMIIの削減)

レート:1Gbpsピンの数:12(デュアル-エッジサンプリング)アプリケーションシナリオ:ギガビットスイッチ、産業用ゲートウェイは100m/1gの柔軟な設計キーポイントと互換性がある必要があります:厳密なタイミング制御が必要です(±1NS偏差耐性)

(4)SGMII(シリアルギガビットMII)

レート:ピンの1g/2.5GbpsNumberの数:2(微分ペア)アプリケーションシナリオ:長距離ボード- - -ボード接続(SERDES経由)高- FPGAとPHYADVANTAGESの間の速度通信:強力な干渉、バックプレーン送信をサポート

(5)USXGMII(ウルトラスピードMII)

レート:ピンの10gbpsNumber:4(微分ペア)アプリケーションシナリオ:マルチ-レートスイッチ(10m/100m/1g/10gアダプティブ)データセンターリーフ-スパインアーキテクチャフィーチャー:低ジッタークロックが必要(<0.5ps RMS)

利点

適切な信頼性戦略は、オンデマンドでカスタマイズできます

製品の信頼性テストは、次の国際基準に厳密に準拠しています。

AEC(自動車エレクトロニクス評議会)

ジェデック(共同電子デバイスエンジニアリング評議会)

MIL(軍事基準)

IEC(国際電気技術委員会)

製品の品質を完全に確保するために、次の5つの側面から製品の信頼性を確保します。

プロセスの信頼性

パッケージングプロセスの信頼性

製品の信頼性

大量生産の信頼性監視

障害分析

に共有します

関連リンク

あなたも好きかもしれません

前の記事

次の記事

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

Subscribe

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy