イーサネット回路設計ガイド

イーサネットインターフェイスハードウェアアーキテクチャの概要

典型的なイーサネットハードウェアインターフェイスは、次の部分で構成されています。

- CPU/MCU:メイン制御システム、上部-層プロトコル処理を担当します。

- Mac(メディアアクセス制御):メディアアクセス制御レイヤーは、データフレームのカプセル化と検証を処理します。

- Phy(物理層):Macによるデジタル信号出力をアナログ電気信号に変換する物理層界面。

- ネットワークトランス(磁気):信号分離、一般的なモード干渉抵抗、およびインピーダンスマッチング関数を提供します。

- RJ45インターフェイス:物理接続ポイント、イーサネット物理メディアへの接続を有効にします。

統合レベルが増加するにつれて、ますます多くのSOC(CHIPのシステム)チップがMACを統合し、PHYを統合している人もいれば、設計方法は常に最適化されています。

- 重要なコンポーネントの分析

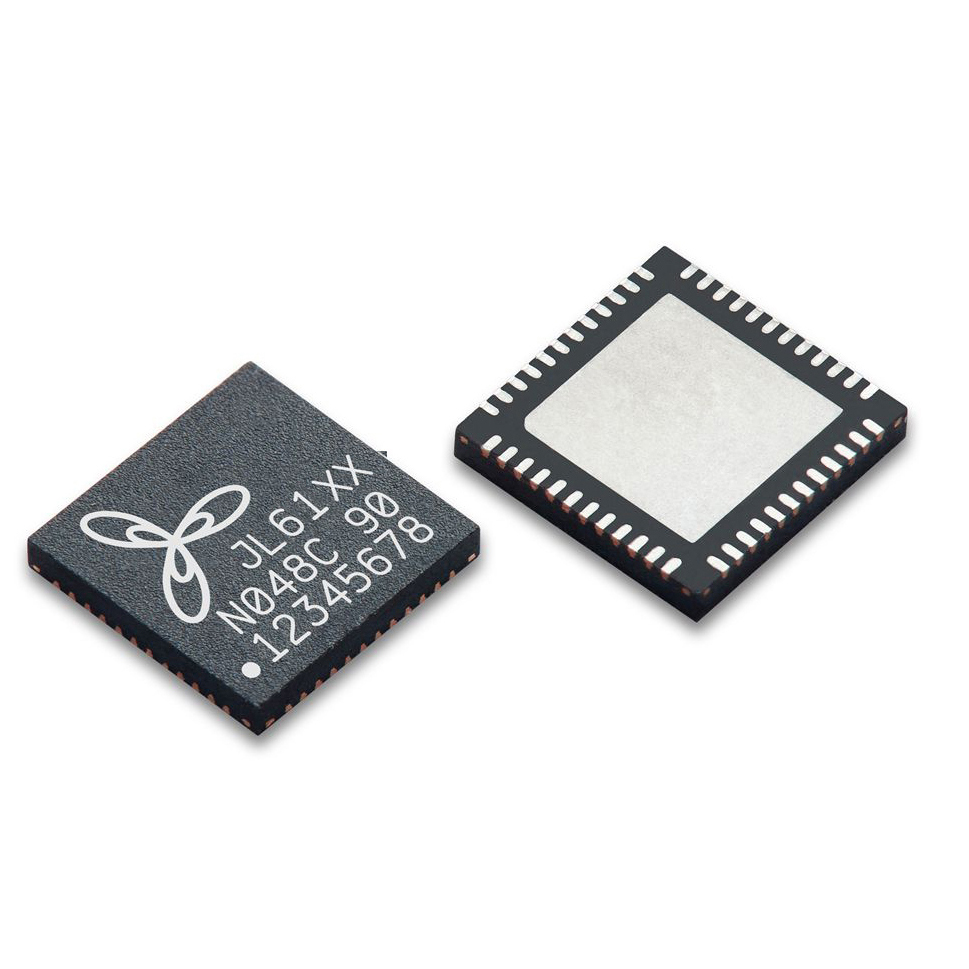

- Phy Chip

- 機能:MAC層のデジタル信号を、ネットワークケーブルを介した送信に適したアナログ信号に変換します。

- 重要なパラメーター:

- 速度:10/100Mbps(100m)、1000Mbps(1g)。

- インターフェイスタイプ:MII/RMII/GMII(MACとの通信)。

- トランスミッション距離:ギガビットイーサネットは、最大100メートルまでのツイストペアトランスミッションをサポートします。

- 特殊機能:一部のPHYチップはPOE(イーサネット上のパワー)をサポートしています。

(ii)ネットワークトランス

- 関数:

- 電気分離:PHYとRJ45の間のDCコンポーネントをブロックして、チップを保護します。

- 一般的なモード干渉の抑制:外部電磁干渉(EMI)が減少します。

- インピーダンスマッチング:信号伝送品質を最適化します。

(iii)RJ45インターフェイス

- 100m(100base - tx):ツイスト-ペアケーブルの2ペア(4 -コア)のみが使用されます(1 - 2、3 - 6ペア以下の仕様ケーブル)、1ペアを使用してデータを送信し、1ペアを使用してデータを受信し、残りの2ペアは使用されません。

- Gigabit(1000Base - T):Twisted -ペアケーブル(CAT5E以降)の4ペア(8ます。

- PCB設計の重要なポイント

- 全体的なレイアウト

- RJ45にできるだけ近くに保ち、微分トレースの長さを短くします。

- 干渉を防ぐために、以下の他の信号行を避けてください。

(ii)微分線(TX/RX)ルーティングルール

- 等しい長さのマッチング(長さの差は5mil以下)。

- インピーダンス制御(通常、100Ω差動インピーダンス)。

- シャープ-角度ルーティングを避けて、信号反射を減らします。

(iii)ネットワークポートとトランスのPCB設計の重要なポイント

- 耐電圧の分離:ネットワークトランスの中央にある分離領域は、電圧要件に耐えるのに十分な広さでなければなりません。 PhyとRJ45は異なる地上飛行機にある必要があり、交差-飛行機のレイアウトまたはルーティングは禁止されています。

- 干渉防止処理:トランスの下のすべての層は、底部の銅箔がノイズを導入するのを防ぐためにくり抜かれています。

- 微分線ルーティング:ネットワークポートシェルグランドレイヤーから離れて、下層を優先します。インピーダンスは、100Ω±10%で制御することをお勧めします(必須ではありませんが推奨)。

- ケーシングの接地:ネットワークポートの金属ケーシングの接地ワイヤは、低-インピーダンス接続を確保するために厚くする必要があります。

- インターフェイス保護設計

- ESD保護デバイス:静電放電が後続の回路に損傷を引き起こすのを防ぐために使用されます。

- サージ保護装置:雷ストライクやその他の要因が回路を損傷するのを防ぐために使用されます。

- 実用的なアプリケーションケース分析

産業用自動化デバイスを例にとると、そのイーサネットインターフェイス設計は、MacとPhyを統合するSOCチップを使用し、合理的なレイアウトとルーティングを通じて安定した信頼できる通信を実現します。実際のアプリケーションでは、デバイスは複雑な電磁環境で安定して動作し、イーサネット通信のための産業自動化の高い要件を満たすことができます。

に共有します

関連リンク

あなたも好きかもしれません

前の記事

次の記事

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

Subscribe

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy