Whitepaper zur Ethernet-PHY-Chip-Technologie

Globale Marktgröße

2023: ca. 1,2 Milliarden US-Dollar (Datenquelle: Yole Développement) Prognose für 2028: mehr als 2,5 Milliarden US-Dollar (CAGR 15,8 %) Wachstumstreiber: Rechenzentrums-Upgrade (400G/800G PHY-Nachfrage) Automobilintelligenz (die Anzahl der PHYs pro Fahrzeug stieg von 1-2 auf 10+) Industrie 4.0 (Durchdringungsrate von industriellem Ethernet übersteigt 50 %)

Regionale Marktverteilung

Nordamerika: 40 % (angetrieben durch Rechenzentren und Automobilelektronik) Asien-Pazifik: 35 % (China ist der wichtigste Wachstumspol, Nachfrage nach 5G-Basisstationen und Elektrofahrzeugen) Europa: 20 % (Industrie 4.0 und ausgereifte Automobilindustriekette)

Marktwettbewerbsmuster

Nordamerika: 40 % (angetrieben durch Rechenzentren und Automobilelektronik) Asien-Pazifik: 35 % (China ist der wichtigste Wachstumspol, Nachfrage nach 5G-Basisstationen und Elektrofahrzeugen) Europa: 20 % (Industrie 4.0 und ausgereifte Automobilindustriekette)

Zukünftige Trends

1. Technologierichtung:

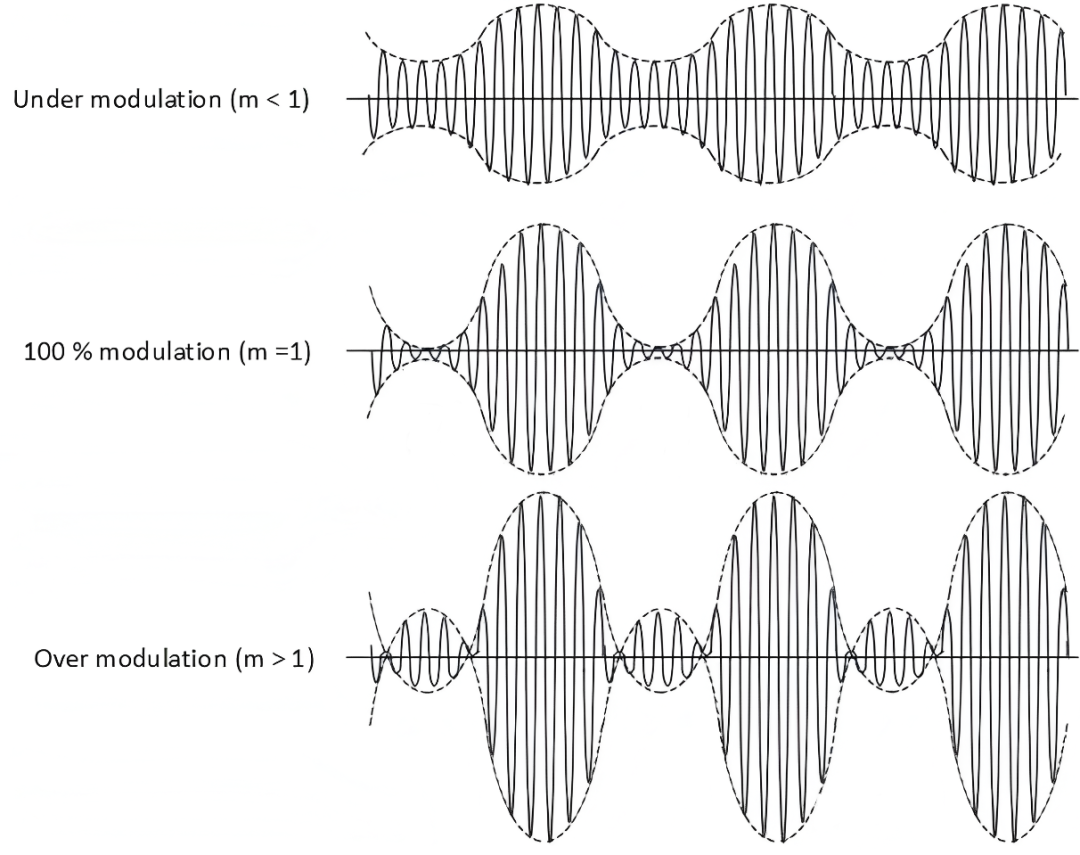

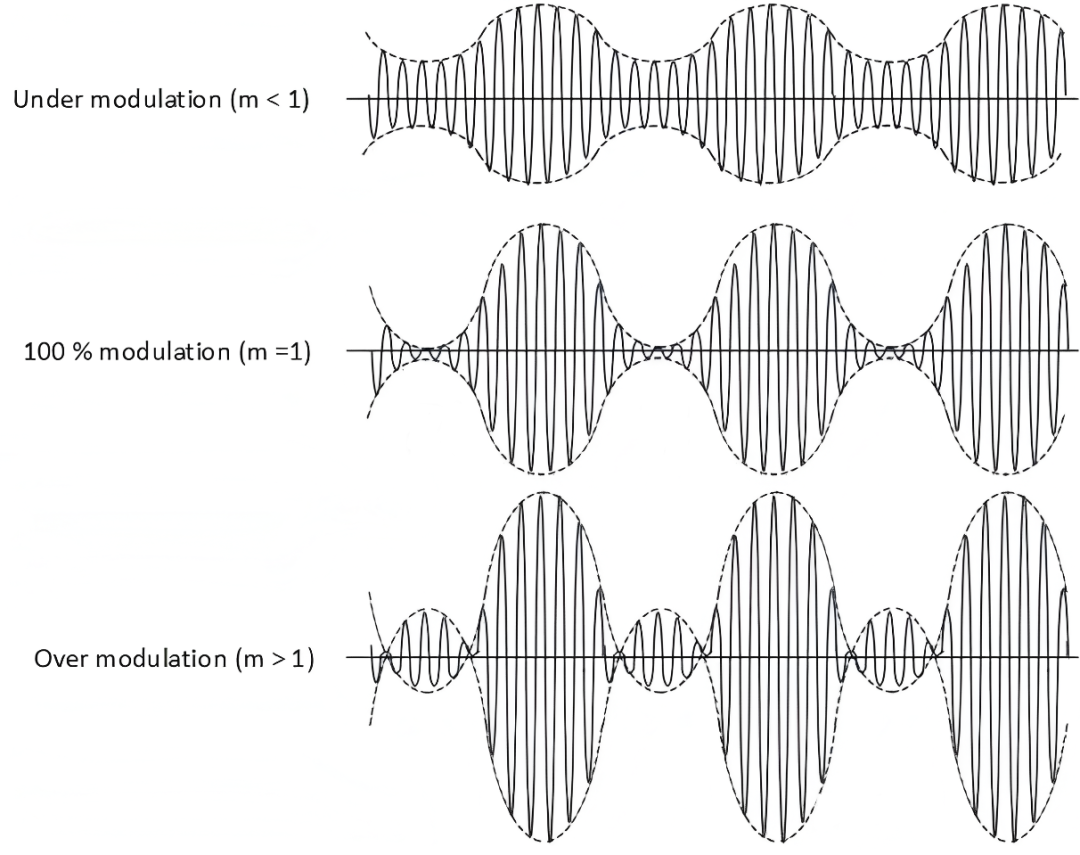

Ultra-hohe Geschwindigkeit: 800G PHY (PAM4-Modulation, Silizium-Photonik-Integration) Geringer Stromverbrauch: 3-nm-Prozess-PHY-Chip (Stromverbrauch um 50 % reduziert) Automotive-Qualität: 10G PHY unterstützt autonomes Fahren L4/L5 (Massenproduktion im Jahr 2025)

2. Veränderungen in der Lieferkette:

Die Vereinigten Staaten beschränken den Export von High-End-PHY nach China und beschleunigen so den Prozess der inländischen Substitution. TSMC/Samsung setzen 3-nm-PHY-Foundry ein, um im High-End-Markt zu konkurrieren.

Verbinden Sie MAC und physische Medien (Kupferkabel/Glasfaser), um eine stabile Netzwerkübertragung zu gewährleisten

1. Signalkonditionierung

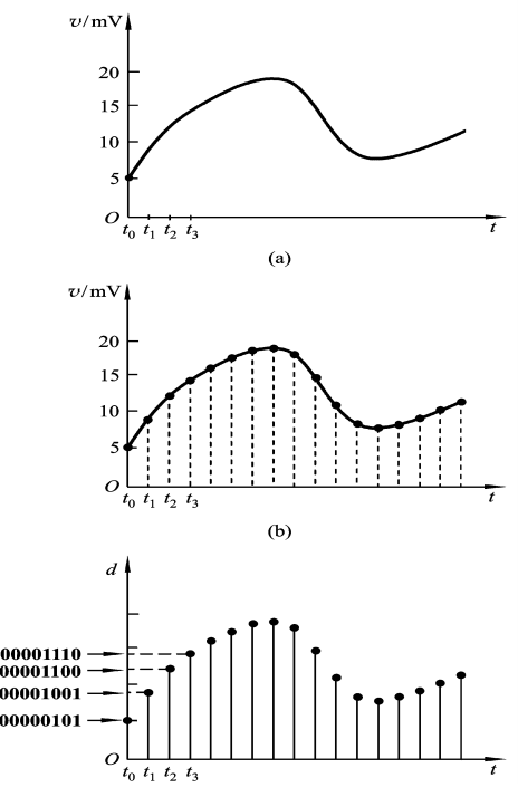

Wandeln Sie die von der MAC-Schicht gesendeten parallelen Daten in einen seriellen Bitstrom um und probieren und dekodieren Sie das empfangene analoge Signal, um es in ein digitales Signal wiederherzustellen.

2. Datenkodierung/-dekodierung

Kompensieren Sie die Dämpfung von Hochfrequenzsignalen in Fernkabeln, beseitigen Sie Intersymbolinterferenzen (ISI) und stellen Sie die Signalwellenform wieder her.

3. Physische Medienschnittstelle

Twisted Pair + Glasfaser + Backplane; integrierter ESD-Schutz und Gleichtaktunterdrückung;

4. Energieverwaltung und Diagnose

Schließen Sie ungenutzte Transceiver-Kanäle im Leerlauf, und der Stromverbrauch kann im Energiesparmodus um 70 % reduziert werden; Es hat die Funktion, Kabelunterbrechungen/Kurzschlüsse/Impedanzanomalien zu erkennen und den Verbindungsstatus zu lesen.

5. Linkverhandlung An den Tarif anpassen

Verhandeln Sie mit dem Peer-Gerät über FLP (Fast Link Pulse) die optimale Rate (10/100/1000 Mbit/s) und stellen Sie schnell eine erneute Verbindung her;

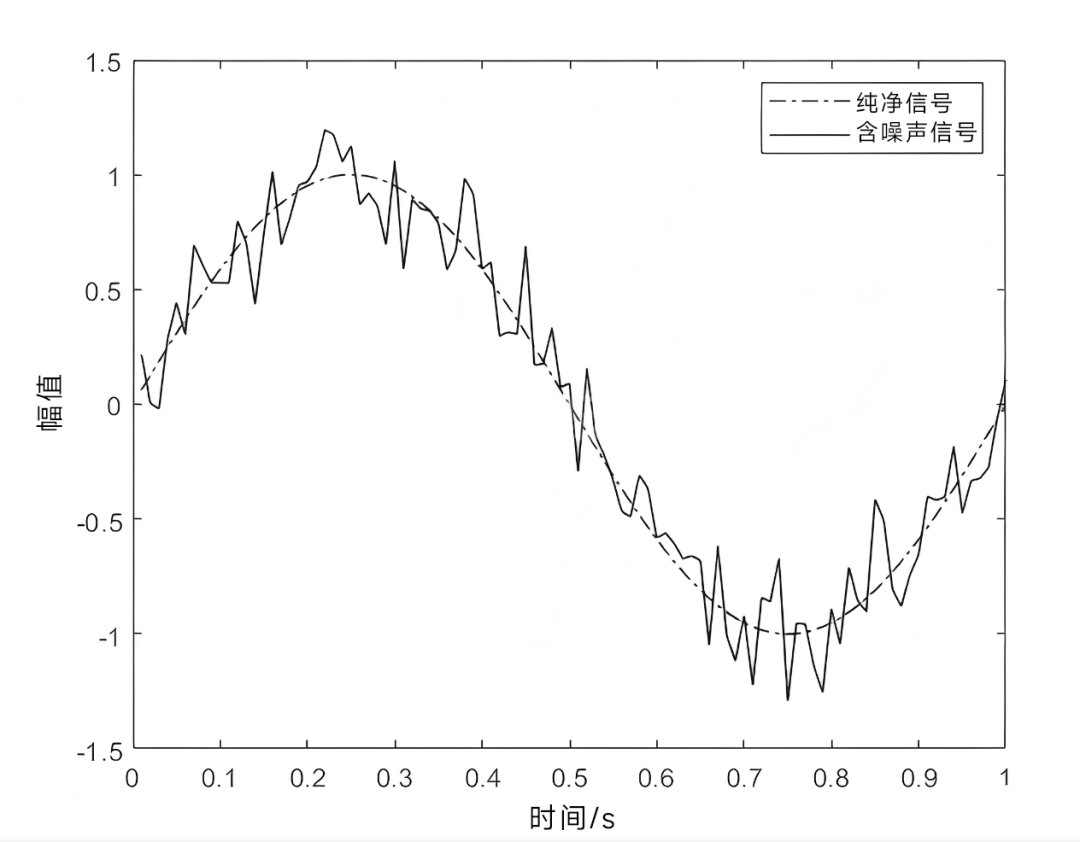

Signalaufbereitung/Datenkodierung und -dekodierung

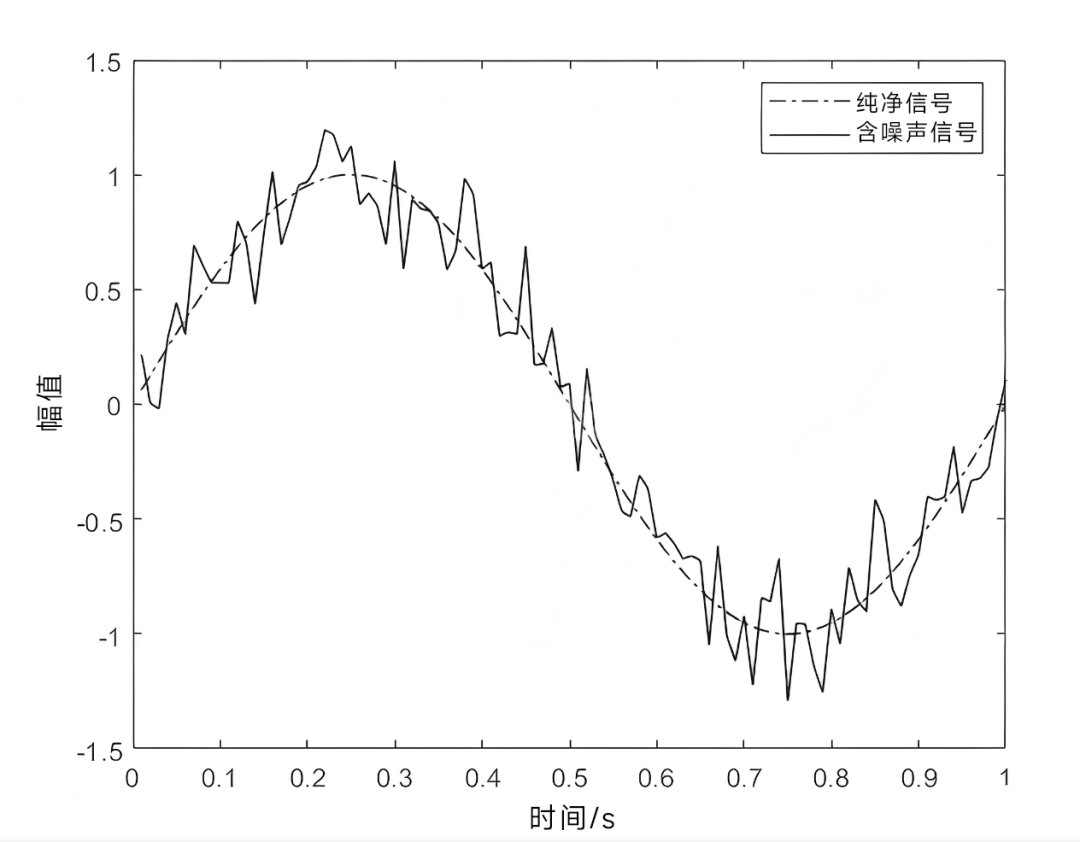

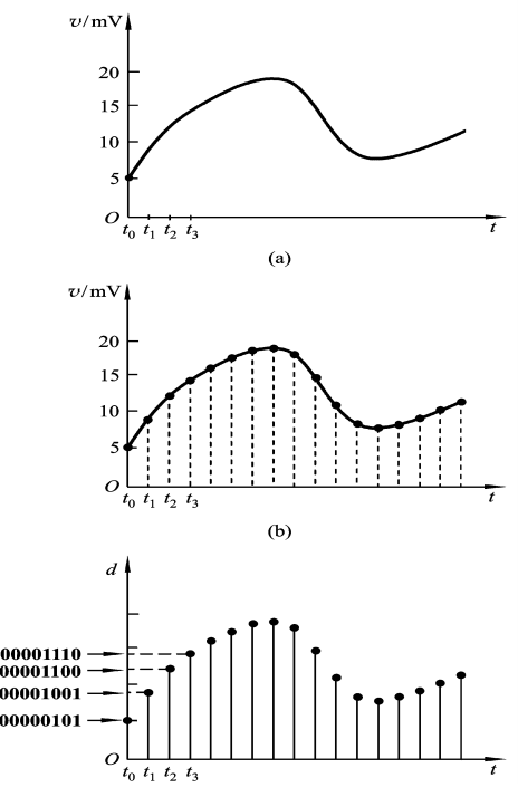

1. Notwendigkeit der Signalkonditionierung

·Anpassung der Signalamplitude: Signalverstärkung für eine einfache Erfassung;·Verbesserung des Signal-Rausch-Verhältnisses: Beseitigung von Rauschinterferenzen elektrischer Signale;·Signalumwandlung: Realisierung der Signalumwandlung durch funktionale Beziehung, was für die Beobachtung erforderlicher Parameter praktisch ist;·Erfüllung der Geräteanforderungen: Signalanpassung;·Erzielung einer Fernübertragung: Anti-Interferenz bei der Fernübertragung;·Schutz der Ausrüstung: Schutz der Back-End-Ausrüstung bei der Messung von Hochspannungssignalen;

2. Signalkonditionierungsprozess (anwendbar für die meisten Fernkommunikationen)

Signalverstärkung -> Filterung -> Signalumwandlung -> Linearisierung -> Isolationsschutz -> Modulation und Demodulation -> Pegelanpassung;

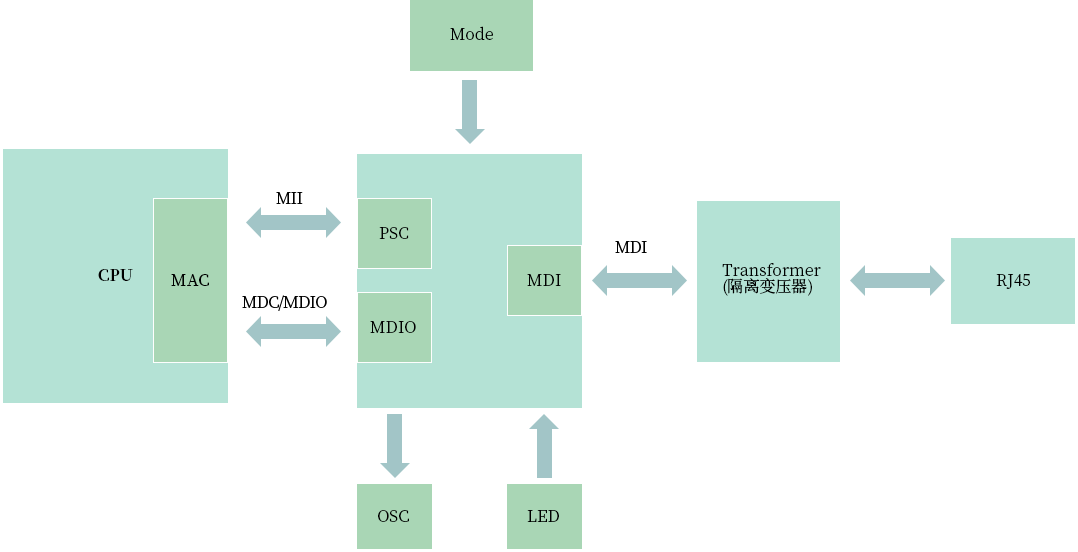

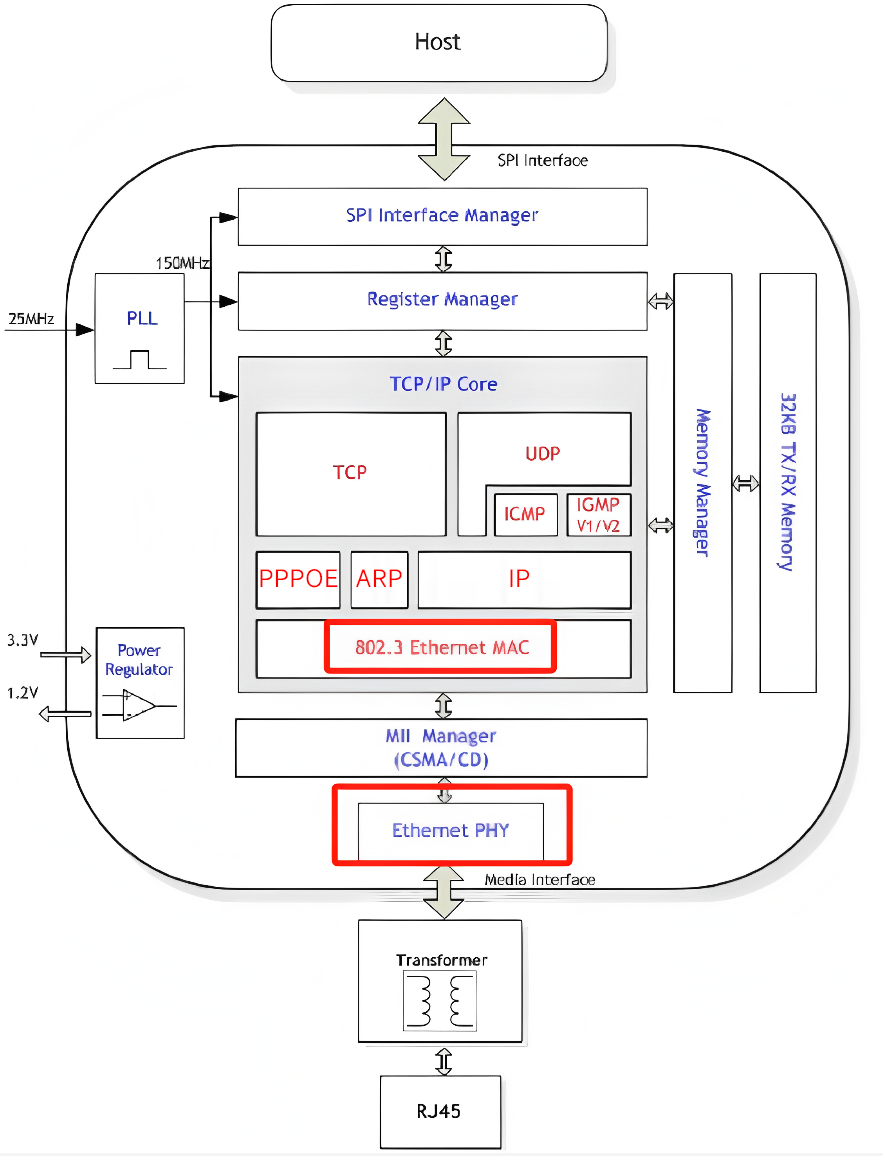

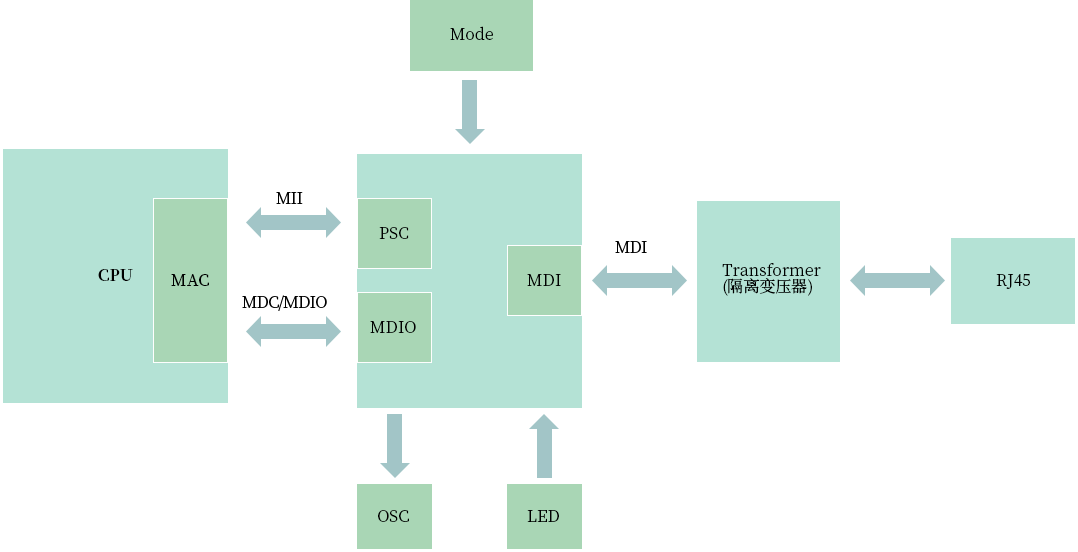

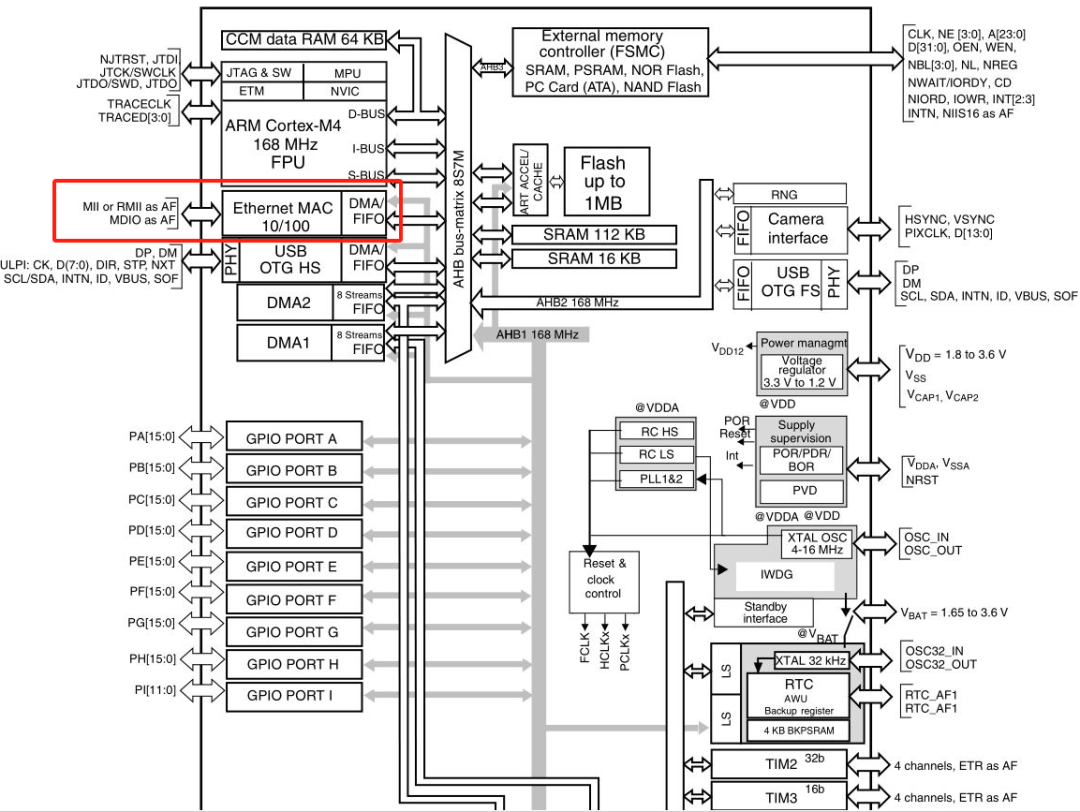

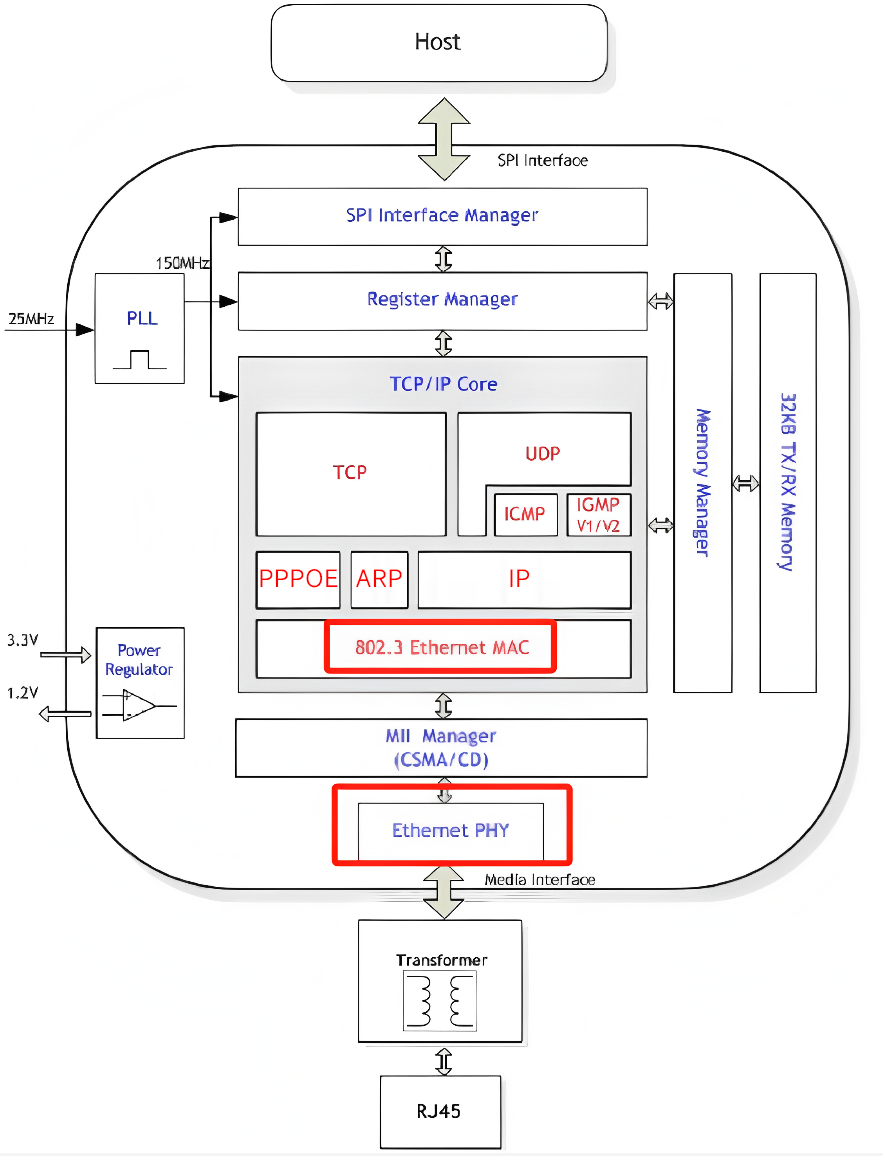

STRUKTURDIAGRAMM

PHY-Chip

Der PHY-Chip (Physical Layer) ist die Kernkomponente der physikalischen Schicht und für das Senden und Empfangen von Ethernet-Signalen verantwortlich. Zu den Hauptfunktionen gehören:

• Signalumwandlung: Wandelt digitale Signale in analoge Signale um, die für die Netzwerkkabelübertragung geeignet sind (Übertragung), und wandelt analoge Signale in digitale Signale um (Empfang).

• Elektrischer Schutz: Bietet zusätzliche elektrische Isolierung durch den Netzwerktransformator, um den PHY-Chip vor Schäden durch äußere Faktoren wie Blitzeinschläge und elektromagnetische Störungen zu schützen.

Netzwerktransformator

• Signalkopplung und -übertragung: Verbessern und übertragen Sie das vom PHY-Chip ausgegebene Differenzsignal durch Differenzialmoduskopplung an das andere Ende des Netzwerkkabels.

• Elektrische Isolierung: Isolieren Sie den DC-Pegelunterschied zwischen dem PHY-Chip und dem Netzwerkkabel, um zu verhindern, dass der Spannungsunterschied zwischen verschiedenen Geräten das Gerät beschädigt.

• Impedanzanpassung: Stellen Sie die Impedanzanpassung zwischen Signalquelle, Last und Übertragungsleitung sicher, um Signalreflexion und Bitfehler zu reduzieren.

• Unterdrückung elektromagnetischer Störungen: Unterdrückung von Gleichtaktstörungen und Reduzierung elektromagnetischer Störungen durch Gleichtaktdrossel (CMC).

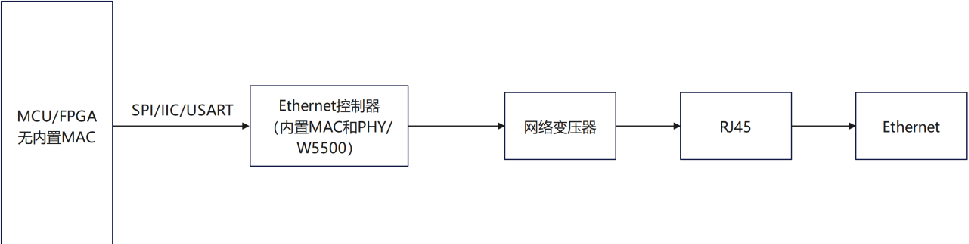

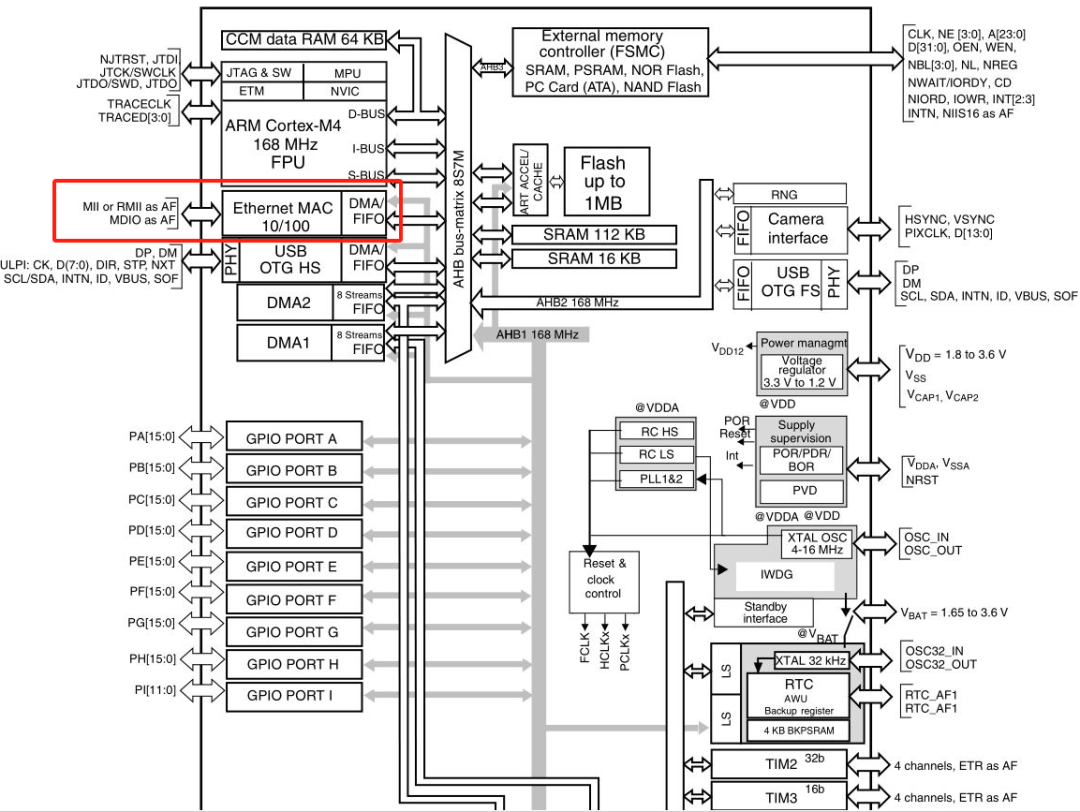

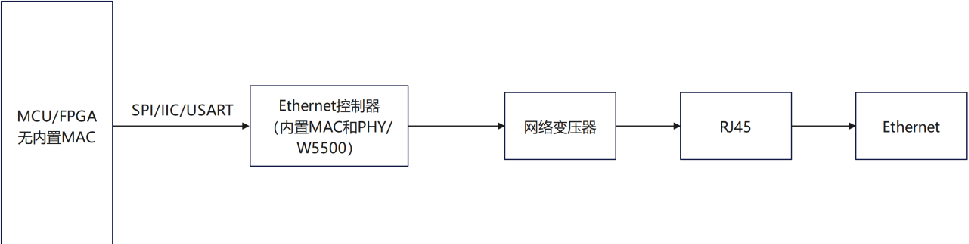

Die oben genannten drei Teile sind nicht unbedingt alle unabhängige Chips. Es gibt hauptsächlich die folgenden Situationen: MAC und PHY sind in die CPU integriert, was schwieriger ist; MAC ist in die CPU integriert und PHY verwendet unabhängige Chips (Mainstream-Lösung); MAC und PHY sind nicht in die CPU integriert und MAC und PHY verwenden unabhängige Chips oder integrierte Chips (High-End-Nutzung);

PARAMETER

1. Bewerten Sie die Unterstützung

• Unterstützter Ratenbereich: Der PHY-Chip muss die von der Zielanwendung benötigte Ethernet-Rate unterstützen, z. B. 10 Mbit/s, 100 Mbit/s, 1 Gbit/s, 10 Gbit/s usw.;

• Adaptive Ratenaushandlung: Unterstützt die Funktion Auto-Negotiation, die automatisch die beste Rate (z. B. 10/100/1000 Mbit/s) und den besten Duplexmodus (Vollduplex/Halbduplex) entsprechend den Fähigkeiten des Peer-Geräts auswählen kann.

2. Schnittstellenstandard

Der PHY-Chip muss mit der oberen MAC-Schicht kompatibel sein. Zu den gängigen Schnittstellen gehören:

• MII: Gilt für 10/100 Mbit/s Ethernet.

• RMII: Vereinfachte Version von MII mit weniger Pins, geeignet für 10/100 Mbit/s.

• GMII: Unterstützt eine Rate von 1 Gbit/s.

• RGMII: Vereinfachte Version von GMII mit weniger Pins, geeignet für 1 Gbit/s.

• SGMII: Serielle Schnittstelle, geeignet für 1 Gbit/s mit weniger Pins.

• Schnittstelle für physikalische Medien (MDI): Unterstützte physikalische Medientypen, wie z. B. Twisted Pair (BASE-T), Glasfaser (BASE-X), Single Twisted Pair (BASE-T1) usw.

3. Übertragungsentfernung

• Übertragungsentfernung: Wählen Sie einen PHY-Chip aus, der die erforderliche Übertragungsentfernung entsprechend den Anwendungsanforderungen unterstützt. Beispielsweise unterstützt 1000BASE-T (Gigabit-Ethernet) die Twisted-Pair-Übertragung bis zu 100 Meter, während Glasfaser-PHY (wie 1000BASE-LX) längere Entfernungen unterstützen kann.

4. Stromverbrauch

• Stromverbrauchsniveau: Ein stromsparendes Design ist entscheidend für Energieeinsparung und Wärmemanagement, insbesondere bei Geräten mit hoher Dichte (z. B. Schaltern) und mobilen Geräten. Beispielsweise kann ein PHY-Chip, der den EEE-Standard (Energy Efficient Ethernet) unterstützt, den Stromverbrauch im Leerlauf senken.

• Thermisches Design: Berücksichtigen Sie die Wärmeableitungsanforderungen des PHY-Chips, insbesondere in Umgebungen mit hohen Temperaturen oder Anwendungen mit hoher Dichte.

5. Zuverlässigkeit und Stabilität

• Elektrische Isolierung: Die elektrische Isolierung wird durch einen Netzwerktransformator erreicht, um den PHY-Chip vor Schäden durch äußere Faktoren wie Blitzeinschläge und elektromagnetische Störungen zu schützen.

• Anti-Interferenz-Fähigkeit: PHY-Chips sollten eine gute elektromagnetische Verträglichkeit (EMV) aufweisen und elektromagnetischen Störungen in industriellen Umgebungen standhalten können. Sie sollten beispielsweise Standards wie CISPR 32 und IEC 61000-4-2 entsprechen.

• Betriebstemperaturbereich: PHY-Chips in Industriequalität unterstützen normalerweise einen breiten Temperaturbereich (z. B. -40 °C–85 °C), um sich an raue Umgebungen anzupassen.

6. Sonderfunktionen

• PoE-Unterstützung: Wenn die Anwendung über ein Ethernet-Kabel mit Strom versorgt werden muss (z. B. IP-Kameras, drahtlose Zugangspunkte), müssen Sie einen Chip auswählen, der PoE (IEEE 80) unterstützt

• Diagnosefunktion: Unterstützt Funktionen wie die Erkennung des Verbindungsstatus und die Überwachung der Signalqualität, um die Netzwerkwartung und Fehlerbehebung zu erleichtern. • Sicherheitsfunktionen: In einigen Anwendungen müssen PHY-Chips möglicherweise Sicherheitsfunktionen wie verschlüsselte Kommunikation oder Authentifizierungsfunktionen unterstützen.

ANWENDUNGSSZENARIO

(1) 10/100 Mbit/s PHY

Anwendungsszenarien: Industrielle Steuerung: SPS, Sensornetzwerk (z. B. Modbus TCP) Smart Home: Smart Socket, Low-Power-IoT-Gerät (z. B. Zigbee-Gateway) On-Board-Diagnose: OBD-II-Schnittstelle (100BASE-T1)

(2) 1 Gbit/s PHY

Anwendungsszenarien: Unterhaltungselektronik: 4K-TV, NAS-Speicher Industriekamera: Bildverarbeitung (Echtzeit-Bildübertragung) Unternehmensnetzwerk: Gigabit-Switch, Router

(3) 2,5G/5G PHY (Multi-Gigabit)

Anwendungsszenarien: Industrielle Steuerung: SPS, Sensornetzwerk (z. B. Modbus TCP) Smart Home: Smart Socket, Low-Power-IoT-Gerät (z. B. Zigbee-Gateway) On-Board-Diagnose: OBD-II-Schnittstelle (100BASE-T1)

(4) 10G/25G PHY

Anwendungsszenarien: Rechenzentrum: Serververbindung (SFP+/QSFP28) 5G-Basisstation: Fronthaul-Netzwerk (eCPRI über 25G) Ultrahochauflösende Videoproduktion: 8K-Video-Echtzeitübertragung

(5) 40G/100G und höher PHY

Anwendungsszenarien: KI/Supercomputing-Cluster: GPU/TPU-Verbindung (InfiniBand-Ersatz) Kern-Backbone-Netzwerk: Metropolregionsnetzwerk/Inter-/Rechenzentrumsverbindung Optische Kommunikation: CPRI/OBSAI-Glasfaser-Fronthaul

DESIGN-WAHLEN

(1) MII (Medienunabhängige Schnittstelle)

Rate: 10/100 Mbit/s Anzahl der Pins: 16+ Anwendungsszenarien: Frühe eingebettete Systeme (z. B. ARM9-Industriesteuerplatinen) Design mit geringer Komplexität (externer MAC-Controller erforderlich) Nachteile: Komplexe Verkabelung, nach und nach durch RMII ersetzt

(2) RMII (reduzierter MII)

Rate: 10/100 Mbit/s Anzahl der Pins: 6 (Daten + Takt) Anwendungsszenarien: Kostenempfindliche Geräte (z. B. Heimrouter) Platzsparendes Design (IoT-Module) Vorteile: Vereinfachte Verkabelung, Unterstützung für 50-MHz-Takt

(3) RGMII (Reduziertes Gigabit MII)

Rate: 1 Gbit/s Anzahl der Pins: 12 (Dual-Edge-Sampling) Anwendungsszenarien: Gigabit-Switches, Industrie-Gateways müssen mit dem flexiblen 100M/1G-Design kompatibel sein. Wichtige Punkte: Eine strenge Timing-Steuerung ist erforderlich (±1 ns Abweichungstoleranz).

(4) SGMII (Serial Gigabit MII)

Rate: 1G/2,5 Gbit/sAnzahl der Pins: 2 (Differenzialpaare)Anwendungsszenarien: Board-zu-Board-Verbindung über große Entfernungen (über SerDes)Hochgeschwindigkeitskommunikation zwischen FPGA und PHYAVorteile: starke Entstörung, Unterstützung der Backplane-Übertragung

(5) USXGMII (Ultra Speed MII)

Rate: 10 Gbit/sAnzahl der Pins: 4 (Differenzialpaare)Anwendungsszenarien: Multi-Rate-Switch (10M/100M/1G/10G adaptiv)Leaf-/Spine-Architektur für RechenzentrenEigenschaften: Takt mit geringem Jitter erforderlich (<0,5ps RMS)

VORTEILE

Entsprechende Zuverlässigkeitsstrategien können bei Bedarf angepasst werden

Der Zuverlässigkeitstest des Produkts entspricht strikt den folgenden internationalen Standards:

2023: ca. 1,2 Milliarden US-Dollar (Datenquelle: Yole Développement) Prognose für 2028: mehr als 2,5 Milliarden US-Dollar (CAGR 15,8 %) Wachstumstreiber: Rechenzentrums-Upgrade (400G/800G PHY-Nachfrage) Automobilintelligenz (die Anzahl der PHYs pro Fahrzeug stieg von 1-2 auf 10+) Industrie 4.0 (Durchdringungsrate von industriellem Ethernet übersteigt 50 %)

Regionale Marktverteilung

Nordamerika: 40 % (angetrieben durch Rechenzentren und Automobilelektronik) Asien-Pazifik: 35 % (China ist der wichtigste Wachstumspol, Nachfrage nach 5G-Basisstationen und Elektrofahrzeugen) Europa: 20 % (Industrie 4.0 und ausgereifte Automobilindustriekette)

Marktwettbewerbsmuster

Nordamerika: 40 % (angetrieben durch Rechenzentren und Automobilelektronik) Asien-Pazifik: 35 % (China ist der wichtigste Wachstumspol, Nachfrage nach 5G-Basisstationen und Elektrofahrzeugen) Europa: 20 % (Industrie 4.0 und ausgereifte Automobilindustriekette)

Zukünftige Trends

1. Technologierichtung:

Ultra-hohe Geschwindigkeit: 800G PHY (PAM4-Modulation, Silizium-Photonik-Integration) Geringer Stromverbrauch: 3-nm-Prozess-PHY-Chip (Stromverbrauch um 50 % reduziert) Automotive-Qualität: 10G PHY unterstützt autonomes Fahren L4/L5 (Massenproduktion im Jahr 2025)

2. Veränderungen in der Lieferkette:

Die Vereinigten Staaten beschränken den Export von High-End-PHY nach China und beschleunigen so den Prozess der inländischen Substitution. TSMC/Samsung setzen 3-nm-PHY-Foundry ein, um im High-End-Markt zu konkurrieren.

PRODUKTMERKMALE

Verbinden Sie MAC und physische Medien (Kupferkabel/Glasfaser), um eine stabile Netzwerkübertragung zu gewährleisten

1. Signalkonditionierung

Wandeln Sie die von der MAC-Schicht gesendeten parallelen Daten in einen seriellen Bitstrom um und probieren und dekodieren Sie das empfangene analoge Signal, um es in ein digitales Signal wiederherzustellen.

2. Datenkodierung/-dekodierung

Kompensieren Sie die Dämpfung von Hochfrequenzsignalen in Fernkabeln, beseitigen Sie Intersymbolinterferenzen (ISI) und stellen Sie die Signalwellenform wieder her.

3. Physische Medienschnittstelle

Twisted Pair + Glasfaser + Backplane; integrierter ESD-Schutz und Gleichtaktunterdrückung;

4. Energieverwaltung und Diagnose

Schließen Sie ungenutzte Transceiver-Kanäle im Leerlauf, und der Stromverbrauch kann im Energiesparmodus um 70 % reduziert werden; Es hat die Funktion, Kabelunterbrechungen/Kurzschlüsse/Impedanzanomalien zu erkennen und den Verbindungsstatus zu lesen.

5. Linkverhandlung An den Tarif anpassen

Verhandeln Sie mit dem Peer-Gerät über FLP (Fast Link Pulse) die optimale Rate (10/100/1000 Mbit/s) und stellen Sie schnell eine erneute Verbindung her;

Signalaufbereitung/Datenkodierung und -dekodierung

1. Notwendigkeit der Signalkonditionierung

·Anpassung der Signalamplitude: Signalverstärkung für eine einfache Erfassung;·Verbesserung des Signal-Rausch-Verhältnisses: Beseitigung von Rauschinterferenzen elektrischer Signale;·Signalumwandlung: Realisierung der Signalumwandlung durch funktionale Beziehung, was für die Beobachtung erforderlicher Parameter praktisch ist;·Erfüllung der Geräteanforderungen: Signalanpassung;·Erzielung einer Fernübertragung: Anti-Interferenz bei der Fernübertragung;·Schutz der Ausrüstung: Schutz der Back-End-Ausrüstung bei der Messung von Hochspannungssignalen;

2. Signalkonditionierungsprozess (anwendbar für die meisten Fernkommunikationen)

Signalverstärkung -> Filterung -> Signalumwandlung -> Linearisierung -> Isolationsschutz -> Modulation und Demodulation -> Pegelanpassung;

STRUKTURDIAGRAMM

PHY-Chip

Der PHY-Chip (Physical Layer) ist die Kernkomponente der physikalischen Schicht und für das Senden und Empfangen von Ethernet-Signalen verantwortlich. Zu den Hauptfunktionen gehören:

• Signalumwandlung: Wandelt digitale Signale in analoge Signale um, die für die Netzwerkkabelübertragung geeignet sind (Übertragung), und wandelt analoge Signale in digitale Signale um (Empfang).

• Elektrischer Schutz: Bietet zusätzliche elektrische Isolierung durch den Netzwerktransformator, um den PHY-Chip vor Schäden durch äußere Faktoren wie Blitzeinschläge und elektromagnetische Störungen zu schützen.

Netzwerktransformator

• Signalkopplung und -übertragung: Verbessern und übertragen Sie das vom PHY-Chip ausgegebene Differenzsignal durch Differenzialmoduskopplung an das andere Ende des Netzwerkkabels.

• Elektrische Isolierung: Isolieren Sie den DC-Pegelunterschied zwischen dem PHY-Chip und dem Netzwerkkabel, um zu verhindern, dass der Spannungsunterschied zwischen verschiedenen Geräten das Gerät beschädigt.

• Impedanzanpassung: Stellen Sie die Impedanzanpassung zwischen Signalquelle, Last und Übertragungsleitung sicher, um Signalreflexion und Bitfehler zu reduzieren.

• Unterdrückung elektromagnetischer Störungen: Unterdrückung von Gleichtaktstörungen und Reduzierung elektromagnetischer Störungen durch Gleichtaktdrossel (CMC).

Die oben genannten drei Teile sind nicht unbedingt alle unabhängige Chips. Es gibt hauptsächlich die folgenden Situationen: MAC und PHY sind in die CPU integriert, was schwieriger ist; MAC ist in die CPU integriert und PHY verwendet unabhängige Chips (Mainstream-Lösung); MAC und PHY sind nicht in die CPU integriert und MAC und PHY verwenden unabhängige Chips oder integrierte Chips (High-End-Nutzung);

PARAMETER

1. Bewerten Sie die Unterstützung

• Unterstützter Ratenbereich: Der PHY-Chip muss die von der Zielanwendung benötigte Ethernet-Rate unterstützen, z. B. 10 Mbit/s, 100 Mbit/s, 1 Gbit/s, 10 Gbit/s usw.;

• Adaptive Ratenaushandlung: Unterstützt die Funktion Auto-Negotiation, die automatisch die beste Rate (z. B. 10/100/1000 Mbit/s) und den besten Duplexmodus (Vollduplex/Halbduplex) entsprechend den Fähigkeiten des Peer-Geräts auswählen kann.

2. Schnittstellenstandard

Der PHY-Chip muss mit der oberen MAC-Schicht kompatibel sein. Zu den gängigen Schnittstellen gehören:

• MII: Gilt für 10/100 Mbit/s Ethernet.

• RMII: Vereinfachte Version von MII mit weniger Pins, geeignet für 10/100 Mbit/s.

• GMII: Unterstützt eine Rate von 1 Gbit/s.

• RGMII: Vereinfachte Version von GMII mit weniger Pins, geeignet für 1 Gbit/s.

• SGMII: Serielle Schnittstelle, geeignet für 1 Gbit/s mit weniger Pins.

• Schnittstelle für physikalische Medien (MDI): Unterstützte physikalische Medientypen, wie z. B. Twisted Pair (BASE-T), Glasfaser (BASE-X), Single Twisted Pair (BASE-T1) usw.

3. Übertragungsentfernung

• Übertragungsentfernung: Wählen Sie einen PHY-Chip aus, der die erforderliche Übertragungsentfernung entsprechend den Anwendungsanforderungen unterstützt. Beispielsweise unterstützt 1000BASE-T (Gigabit-Ethernet) die Twisted-Pair-Übertragung bis zu 100 Meter, während Glasfaser-PHY (wie 1000BASE-LX) längere Entfernungen unterstützen kann.

4. Stromverbrauch

• Stromverbrauchsniveau: Ein stromsparendes Design ist entscheidend für Energieeinsparung und Wärmemanagement, insbesondere bei Geräten mit hoher Dichte (z. B. Schaltern) und mobilen Geräten. Beispielsweise kann ein PHY-Chip, der den EEE-Standard (Energy Efficient Ethernet) unterstützt, den Stromverbrauch im Leerlauf senken.

• Thermisches Design: Berücksichtigen Sie die Wärmeableitungsanforderungen des PHY-Chips, insbesondere in Umgebungen mit hohen Temperaturen oder Anwendungen mit hoher Dichte.

5. Zuverlässigkeit und Stabilität

• Elektrische Isolierung: Die elektrische Isolierung wird durch einen Netzwerktransformator erreicht, um den PHY-Chip vor Schäden durch äußere Faktoren wie Blitzeinschläge und elektromagnetische Störungen zu schützen.

• Anti-Interferenz-Fähigkeit: PHY-Chips sollten eine gute elektromagnetische Verträglichkeit (EMV) aufweisen und elektromagnetischen Störungen in industriellen Umgebungen standhalten können. Sie sollten beispielsweise Standards wie CISPR 32 und IEC 61000-4-2 entsprechen.

• Betriebstemperaturbereich: PHY-Chips in Industriequalität unterstützen normalerweise einen breiten Temperaturbereich (z. B. -40 °C–85 °C), um sich an raue Umgebungen anzupassen.

6. Sonderfunktionen

• PoE-Unterstützung: Wenn die Anwendung über ein Ethernet-Kabel mit Strom versorgt werden muss (z. B. IP-Kameras, drahtlose Zugangspunkte), müssen Sie einen Chip auswählen, der PoE (IEEE 80) unterstützt

• Diagnosefunktion: Unterstützt Funktionen wie die Erkennung des Verbindungsstatus und die Überwachung der Signalqualität, um die Netzwerkwartung und Fehlerbehebung zu erleichtern. • Sicherheitsfunktionen: In einigen Anwendungen müssen PHY-Chips möglicherweise Sicherheitsfunktionen wie verschlüsselte Kommunikation oder Authentifizierungsfunktionen unterstützen.

ANWENDUNGSSZENARIO

(1) 10/100 Mbit/s PHY

Anwendungsszenarien: Industrielle Steuerung: SPS, Sensornetzwerk (z. B. Modbus TCP) Smart Home: Smart Socket, Low-Power-IoT-Gerät (z. B. Zigbee-Gateway) On-Board-Diagnose: OBD-II-Schnittstelle (100BASE-T1)

(2) 1 Gbit/s PHY

Anwendungsszenarien: Unterhaltungselektronik: 4K-TV, NAS-Speicher Industriekamera: Bildverarbeitung (Echtzeit-Bildübertragung) Unternehmensnetzwerk: Gigabit-Switch, Router

(3) 2,5G/5G PHY (Multi-Gigabit)

Anwendungsszenarien: Industrielle Steuerung: SPS, Sensornetzwerk (z. B. Modbus TCP) Smart Home: Smart Socket, Low-Power-IoT-Gerät (z. B. Zigbee-Gateway) On-Board-Diagnose: OBD-II-Schnittstelle (100BASE-T1)

(4) 10G/25G PHY

Anwendungsszenarien: Rechenzentrum: Serververbindung (SFP+/QSFP28) 5G-Basisstation: Fronthaul-Netzwerk (eCPRI über 25G) Ultrahochauflösende Videoproduktion: 8K-Video-Echtzeitübertragung

(5) 40G/100G und höher PHY

Anwendungsszenarien: KI/Supercomputing-Cluster: GPU/TPU-Verbindung (InfiniBand-Ersatz) Kern-Backbone-Netzwerk: Metropolregionsnetzwerk/Inter-/Rechenzentrumsverbindung Optische Kommunikation: CPRI/OBSAI-Glasfaser-Fronthaul

DESIGN-WAHLEN

(1) MII (Medienunabhängige Schnittstelle)

Rate: 10/100 Mbit/s Anzahl der Pins: 16+ Anwendungsszenarien: Frühe eingebettete Systeme (z. B. ARM9-Industriesteuerplatinen) Design mit geringer Komplexität (externer MAC-Controller erforderlich) Nachteile: Komplexe Verkabelung, nach und nach durch RMII ersetzt

(2) RMII (reduzierter MII)

Rate: 10/100 Mbit/s Anzahl der Pins: 6 (Daten + Takt) Anwendungsszenarien: Kostenempfindliche Geräte (z. B. Heimrouter) Platzsparendes Design (IoT-Module) Vorteile: Vereinfachte Verkabelung, Unterstützung für 50-MHz-Takt

(3) RGMII (Reduziertes Gigabit MII)

Rate: 1 Gbit/s Anzahl der Pins: 12 (Dual-Edge-Sampling) Anwendungsszenarien: Gigabit-Switches, Industrie-Gateways müssen mit dem flexiblen 100M/1G-Design kompatibel sein. Wichtige Punkte: Eine strenge Timing-Steuerung ist erforderlich (±1 ns Abweichungstoleranz).

(4) SGMII (Serial Gigabit MII)

Rate: 1G/2,5 Gbit/sAnzahl der Pins: 2 (Differenzialpaare)Anwendungsszenarien: Board-zu-Board-Verbindung über große Entfernungen (über SerDes)Hochgeschwindigkeitskommunikation zwischen FPGA und PHYAVorteile: starke Entstörung, Unterstützung der Backplane-Übertragung

(5) USXGMII (Ultra Speed MII)

Rate: 10 Gbit/sAnzahl der Pins: 4 (Differenzialpaare)Anwendungsszenarien: Multi-Rate-Switch (10M/100M/1G/10G adaptiv)Leaf-/Spine-Architektur für RechenzentrenEigenschaften: Takt mit geringem Jitter erforderlich (<0,5ps RMS)

VORTEILE

Entsprechende Zuverlässigkeitsstrategien können bei Bedarf angepasst werden

Der Zuverlässigkeitstest des Produkts entspricht strikt den folgenden internationalen Standards:

AEC (Rat für Automobilelektronik)

JEDEC(Gemeinsamer Rat für Elektronengerätetechnik)

MIL (Militärstandard)

IEC (Internationale Elektrotechnische Kommission)

Um die Produktqualität vollständig sicherzustellen, gewährleisten wir die Produktzuverlässigkeit unter folgenden fünf Gesichtspunkten:

Prozesssicherheit

Zuverlässigkeit des Verpackungsprozesses

Produktzuverlässigkeit

Überwachung der Zuverlässigkeit der Massenproduktion

Fehleranalyse

teilen zu

Verwandte Links

Vielleicht gefällt es Ihnen auch

Vorheriger Artikel

Nächster Artikel

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

Subscribe

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy