Auswahl von Chipplan- und Netzwerktransformatoren

Auswahl von Chipplan- und Netzwerktransformatoren

Im Folgenden finden Sie einen umfassenderen technischen Vergleich und eine Designanalyse von kapazitiven/induktiven Chip-LAN- und integrierten Netzwerktransformatoren. Der Inhalt ist etwa doppelt so umfassend wie die ursprüngliche Version und enthält eine Analyse der internen Struktur des Geräts, praktischere Beschreibungen von Designherausforderungen und Fälle von Branchenanwendungstechnologie:

──────────────────────── ────────────────────────

Teil 1: Kapazitives Chip-LAN vs. integrierter Netzwerktransformator - Eine systematische Analyse vom Prinzip bis zur Umsetzung

1. Gerätestruktur und physikalisches Prinzip

Kapazitives Chip-LAN:

- Architekturzerlegung:

- Als Isolationsschicht dienen intern integrierte Hochspannungs-Keramikkondensatoren (Spannungsfestigkeit 1-2kV) mit beidseitig angeschlossenen Differential-Signalübertragungsnetzen.

- Wird mit ESD-Schutzdioden und Mikro-Gleichtaktinduktivitäten zur Unterdrückung von Spannungsspitzen und elektromagnetischen Störungen geliefert.

- Typisches Gehäuse: 0402/0603-Chipgehäuse, vollständiges SMD-Design, kein Magnetkern.

- Signalpfadmodell:

- Stellt für hohe Frequenzen eine niedrige Impedanz dar und lässt Signale durch, der Gleichstrompfad wird jedoch durch den Kondensator blockiert.

- Parasitäre Induktivität (ca. 1-2nH) und verteilte Kapazität (0,5-1pF) wirken sich direkt auf die Dämpfung von Signalen über 10G aus.

Integrierter Netzwerktransformator:

- Architekturzerlegung:

- Magnetischer Isolationskern: Ferritmagnetischer Ringkern oder Planartransformatorstruktur, Primär-Sekundär-Wicklungsverhältnis 1:1 (oder kundenspezifisch).

- Peripherieschaltung: Eingebautes Chip-RC-Netzwerk zum Ausgleich der Gleichtaktimpedanz; einige Module verfügen über eine Gleichtaktdrossel (CMC).

- Paket: DIP/SMD-Modul (Größe 6x6mm bis 15x15mm) mit Metallabschirmung.

- Wirkungsgrad der magnetischen Kopplung:

- Die anfängliche Permeabilität (μi) und die Sättigungsflussdichte (Bs) des Kernmaterials bestimmen die Bandbreite und die Leistungsfähigkeit.

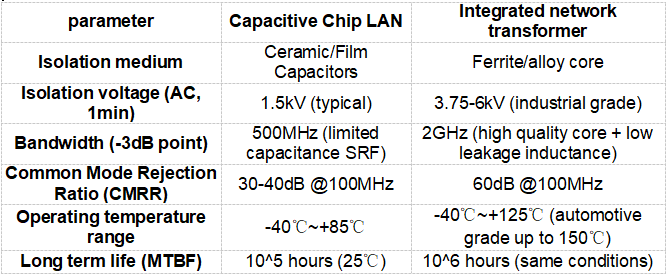

Vergleich der wichtigsten Parameter: Kondensatortyp vs. Transformatortyp

──────────────────────── ────────────────────────

2. Tiefgreifende Herausforderungen und Lösungen für das Hardware-Design

(1) Risiken beim kapazitiven Chip-LAN-Design

- Kondensator hält Spannungsabfall stand:

- Wiederholtes Laden und Entladen mit hoher Frequenz und hoher Spannung (z. B. bei PoE-Anwendungen) führt zu einer Alterung des Kondensatordielektrikums und einem erhöhten Leckstrom.

- Gegenmaßnahme: Wählen Sie hochstabile Keramikkondensatoren wie X7R/X8R und reservieren Sie einen Spannungsspielraum von 20 %.

- Hochfrequenzverlustkontrolle:

- Wenn die Signalfrequenz > 1 GHz ist, begrenzt die Eigenresonanzfrequenz (SRF) des Kondensators die effektive Bandbreite.

- Gegenmaßnahmen: Verkürzen Sie die Leiterbahnlänge vom PHY zum Kondensator (<5 mm), deaktivieren Sie Durchkontaktierungen und rechtwinklige Drehungen.

(2) Designrisiken des integrierten Netzwerktransformators

- Problem der magnetischen Sättigung:

- In Hochleistungsszenarien wie PoE++ (90 W) verursachen große Ströme eine Kernsättigung und explodierende Verluste.

- Gegenmaßnahmen: Wählen Sie Sendust- oder nanokristalline Kerne mit hohen Bs-Werten und vergrößern Sie den Luftspalt (Opferinduktivität).

- Störungen durch hochfrequente Strahlung:

- Ungeschirmte Transformatoren werden zu Strahlungsquellen im GHz-Band und beeinträchtigen HF-Schaltkreise (z. B. Wi-Fi/BT-Module).

- Gegenmaßnahmen: Modulgehäuse erden und magnetische Absorptionsmaterialien (z. B. Ferritbleche) darum herum anordnen.

──────────────────────── ────────────────────────

3. Anpassung der Anwendungsszenario-Technologie und typische Fälle

(1) Flexible Anwendung von kapazitivem Chip-LAN

- Schnelles Laden und Datenübertragung zwei-in-eins (USB PD + Ethernet):

- Verwenden Sie in einer USB-Typ-C-Dockingstation kapazitives LAN, um Platz zu sparen und gleichzeitig eine Stromversorgung von 100 W zu unterstützen.

- Designschwierigkeit: PD-Protokollkommunikation (CC-Leitung) und Differenzsignal müssen streng isoliert werden, um kapazitives Kopplungsrauschen zu verhindern.

- Industrielles IoT-Low-Power-Sensornetzwerk:

- Im RS-485-zu-Ethernet-Gateway erfüllt die Kondensatorisolation die grundlegende Spannungsfestigkeit von 2 kV und es gibt keine Kernhysterese bei -40℃ Tieftemperaturstart.

(2) High-End-Anwendungen integrierter Transformatoren

- 800G optisches Modul SerDes-Schnittstellenisolierung:

- Verwenden Sie Ultra-Wideband-Transformatoren (unterstützt 56G PAM4) und kombinieren Sie diese mit Lineartreibern, um Verluste auszugleichen.

- SI-Verifizierung: Verwenden Sie TDR (Zeitbereichsreflektometer), um eine Impedanzanpassung und einen PCB-Routing-Fehler innerhalb von ±5 % sicherzustellen.

- Gigabit-Ethernet-Backbone für Elektrofahrzeuge:

- Mechanische Verstärkung von Kern und Spule, Epoxidharzverguss zur Vermeidung von Bruch bei Vibration und Temperaturschock.

──────────────────────── ────────────────────────

Teil 2: Induktives Chip-LAN vs. integrierter Netzwerktransformator - Durchbruch in der Hochfrequenzleistung und -zuverlässigkeit

1. Technologische Innovation des induktiven Chip-LAN

(1) Fusion von magnetischer Integration und Halbleitertechnologie

- 3D-Stapelinduktor-Technologie:

- Verwenden Sie TSV (Through Silicon Via), um Spiralinduktivitäten auf Siliziumsubstraten herzustellen, wodurch der Q-Wert um 30 % erhöht wird und 10 GHz Ultra-Breitband unterstützt wird.

- Typische Hersteller: TDKs MLP-Serie (Multi-Layer Pieced Inductor).

- Magnetische und elektrische Verbundisolierung:

- Induktive Isolierung + kapazitive Kopplung mit zwei Pfaden, redundantes Design verbessert das EMV-Niveau (z. B. Erfüllung von CISPR 32 Klasse B).

(2) Leistungsgrenzen von induktiven Transformatoren im Vergleich zu herkömmlichen Transformatoren

──────────────────────── ────────────────────────

2. Hochfrequenzfallen und Cracking-Methoden im Hardware-Design

(1) Signalklingelunterdrückung für induktives Chip-LAN

- Grundursache:

- Signalflanken mit hoher Geschwindigkeit (<100 ps) lösen eine LC-Resonanz aus, und das Überschwingen führt zu einem Anstieg der Bitfehlerrate (BER).

- Gegenmaßnahmen:

- Fügen Sie einen 22-Ω-Widerstand (oder ein einstellbares Abschlussnetzwerk) in Reihe auf der PHY-Seite hinzu, um die Impedanz des Treibers anzupassen.

- Optimierung des Leiterplattenstapels: Die Referenzebene ist vollständig (Kreuzsegmentierung vermeiden) und der Abstand zwischen Signalschicht und GND-Schicht beträgt <4 mil.

(2) Multiport-Nebensprechsteuerung des integrierten Transformators

- Grundursache:

- Die Magnetfeldkopplung von Multiport-Transformatoren in Schaltern verschlechtert das Far-End-Crosstalk (FEXT).

- Gegenmaßnahmen:

- Der Modulabstand beträgt ≥10 mm und zwischen den Signalschichten ist eine abgeschirmte Masseebene eingefügt (Streifenleitungsstruktur).

- Serielle Anschlüsse sind versetzt angeordnet, wodurch die symmetrische Kopplung unterbrochen wird.

──────────────────────── ────────────────────────

3. Branchenführende Anwendungen und Technologietrends

(1) SiP-Integration von induktivem Chip-LAN

- Heterogene Integrationsfälle:

- Intel „Ethernet SiP“: PHY-Chip, Induktorisolierung und TVS sind in einem 5x5-mm-Gehäuse mit einer Rate von 2,5 Gbit/s integriert.

- Vorteile: Reduzierung der Leiterplattenfläche um 60 % und Steigerung der Ausbeute auf 99,8 % (herkömmliche Module 97 %).

(2) Magneto-optische Hybrid-Isolationstechnologie

- Technische Route:

- VCSEL (Vertical Cavity Surface Laser) und Fotodiode sind in den Magnetkreis des Transformators eingebettet, um eine elektrische/magnetische/optische Dreifachisolierung zu erreichen.

- Hält Spannungen über 30 kV stand und wurde in UHV-Überwachungssystemen für Umspannwerke eingesetzt.

(3) Forschung und Entwicklung von Quantenpunkt-Magnetkernen

- Innovation:

- Quantenpunktdotierte magnetische Materialien reduzieren Hochfrequenzverluste um 50 % und unterstützen Prototypen der 1-THz-Terahertz-Kommunikation.

- Mögliche Szenarien: 6G-Wireless-Backhaul-Netzwerk, hochpräzise Radarinterferenzisolierung.

──────────────────────── ────────────────────────

4. Entscheidungsbaum für die Ingenieurauswahl

Schritt 1: Anforderungen priorisieren

- Isolationsspannungsfestigkeit > 3kV? → Wählen Sie einen Transformator aus

- Raumkostenempfindlich? → Wählen Sie kapazitiv

- Rate > 10 Gbit/s? → Wählen Sie einen Transformator oder einen erweiterten Induktor

- Benötigen Sie eine Automobilzertifizierung? → Wählen Sie den AEC-Q200-Transformator

Schritt 2: Überprüfen Sie die Stabilität der Lieferkette

- Kapazitives Chip-LAN: Der Lieferzyklus taiwanesischer Hersteller (Yageo/Walsin) beträgt 8 Wochen und die Ausbeute inländischer Alternativen (Fenghua) muss verbessert werden.

- Integrierter Transformator: TDK/Murata aus Japan hat eine Lieferzeit von 12 Wochen, und die inländische Alternative Magnetron Technology muss die langfristige Zuverlässigkeit bewerten.

Schritt 3: Vorläufiges Forschungs- und Testprojekt

- Erforderliche Elemente: Isolationsspannungstest, TDR-Impedanzüberprüfung, Wärmezyklus (-55℃~+125℃ 1000 Mal)

- Optionale Elemente: HBM ESD-Test, Salzsprühkorrosionstest (Schiffsausrüstung), zufällige Vibrationsanalyse (Fahrzeug-montiert).

──────────────────────── ────────────────────────

Zusammenfassen

Kapazitives/induktives Chip-LAN und integrierter Netzwerktransformator haben jeweils ihre eigenen technischen Vorteile:

- Miniaturisierung und Kosten: Kondensator-/Induktor-Chip-LAN dominiert die Unterhaltungselektronik und das leichte IoT.

- Extreme Zuverlässigkeit und Leistung: Integrierte Transformatoren sind immer noch die beste Wahl für Industrie-, Automobil- und Militäranwendungen.

- Künftiges Schlachtfeld: 3D-Magnetintegration, Quantenmagnetkern und magnetooptische Hybridisolationstechnologie werden die Industrielandschaft neu gestalten.

Design-Motto: „Isolationsniveau und Signalintegrität sind die obersten Prinzipien, alles andere ist ein Kompromiss.“

Newsletter subscription

Subscribe to our newsletter and stay updated on the latest information of our company and product.

Name

|

I agree that the information that I provide will be used in accordance with the terms of Voohu International Inc. Privacy & Cookies Policy